在过去的20年中,个人计算机及手机的发展驱动半导体技术不断进步,先后创造了互联网时代和移动互联网时代,当前,云计算、大数据、人工智能、5G、物联网等成为新的发展热点,正在掀起信息技术创新的新高潮。半导体工艺及制造装备作为整个电子信息产业的基础,为信息技术持续进步提供了发展动力。在集成电路方面,半导体工艺及制造装备沿摩尔定律和超越摩尔定律2个方向发展,支撑了更高性能、更低功耗、更低成本、更高集成度的电子产品制造;在分立器件方面,半导体工艺及制造装备不断满足以第三代半导体为代表的新材料、新器件制造需求。本文面向信息产业技术发展趋势,从集成电路工艺设备、分立器件制造设备2个方面对半导体工艺及制造装备技术发展趋势进行了综述及展望。

1 应用驱动工艺与装备技术进步

1.1 摩尔定律持续演进

云计算、大数据、移动设备、物联网等新一代信息技术对以逻辑器件、存储器等为代表的集成电路性能、功耗、成本和集成度提出了更高的要求,推动摩尔定律持续演进,例如:云计算、大数据等高性能计算应用侧重于性能改善;移动设备、物联网等应用侧重于性能改善、成本降低和能耗降低。

根据国际电子器件与系统技术路线图(International Roadmap For Devices And Systems, IRDS),摩尔定律持续演进要求集成电路每两到三年实现性能、功能、集成度和成本等方面的进步。在性能方面,工作电压降低的情况下,工作频率提升15%;在功耗方面,性能不变的情况下,开关能耗减少30%;在集成度方面,芯片面积减小30%;在成本方面,尺寸微缩的同时减少15%的芯片成本[1]。

为满足集成电路性能演进的要求,集成电路制造工艺及装备技术,尤其是集成电路前道工艺设备,包括光刻机、刻蚀机、离子注入机、薄膜设备、扩散设备、化学机械平坦化设备(Chemical Mechanical Polishing, CMP)、电化学沉积设备(Electrochemistry Deposition, ECD)、湿法工艺设备等八大类设备制造能力将由当前的5 nm节点进一步推进发展,经3 nm、2.1 nm、1.5 nm直至1 nm(等效)、0.7 nm(等效)节点。最主要的技术发展方向包括:极紫外(Extreme Ultraviolet, EUV)光刻设备、围栅晶体管(Gate-All-Around, GAA)制备设备、设备智能化、450 mm(18英寸)晶圆设备等,越来越强调高精度、原子级加工等技术能力。

1.2 系统集成及超越摩尔定律

当前集成电路特征尺寸已经向1 nm节点迈进,逐渐逼近物理极限,摩尔定律面临失效,更加强调多功能集成的超越摩尔定律开始登上舞台。一方面,Chiplet技术通过将复杂的片上系统(System on Chip, 缩写为SoC)芯片拆分,以合适的制程完成“小芯片”制造,并在封装层面完成系统集成,为复杂SoC芯片日益增加的成本控制和质量控制问题提供了一种解决方案;另一方面,不同材料、结构的器件往往具有独特的功能优势,利用微电子工艺实现多种功能、不同材料器件的集成,使之成为能完成一定任务的系统芯片,称为集成微系统,其在医药及可穿戴设备、汽车电子、移动设备、航天等领域已经展现出了巨大的应用潜力。

在系统集成及超越摩尔定律领域, DAPRA(美国国防部高级研究计划局)先后发布了异构集成(Diverse Accessible Heterogeneous Integration,简称DAHI,旨在建立基于硅衬底及CMOS工艺的多种材料及器件集成技术)项目、三维单片系统芯片(Three dimensional monolithic system on chip,简称3D SoC,旨在探索逻辑、存储等功能在同一芯片上三维集成的技术)项目、以及正在执行的CHIPS项目(旨在形成标准化的系统集成模块、集成界面及相应的产业生态系统),这些项目体现的技术发展需求主要包括:多功能组件的系统集成、3D集成及相关的标准化及生态建设工作[2]。

根据国际异质集成技术路线图(Heterogeneous integration roadmap,HIR)[3],系统级封装(System in package, 缩写为SiP)、2.5D/3D集成以及晶圆级封装(Wafer-level-package,缩写为WLP)是集成电路后道封装及微系统领域最重要的技术发展趋势。其中SiP强调多功能组件的集成;2.5D/3D集成强调芯片在垂直方向的堆叠;WLP强调大量裸芯片在同一衬底上的一次性封装成形。SiP、2.5D/3D集成、WLP的理念在实际应用中可能交叉出现,三者的支撑工艺设备主要是芯片封装设备,如减薄设备、键合设备(包括倒装键合和引线键合)、划切设备等,此外还包括基于光刻、刻蚀、薄膜等芯片硅通孔(Through-Silicon-Via,缩写为TSV)制造的工艺设备等[3]。这些工艺设备技术发展需要适应SiP、2.5D/3D集成及WLP工艺发展的需要,最主要的技术特征是前道设备的广泛应用和前后道技术的融合发展。

1.3 基于新材料的分立器件创新

如今随着集成电路及集成微系统技术不断进步,由于新材料体系带来的优越性能,分立器件具有独特的生命力。以HgCdTe和InAs/GaSb II类超晶格为代表的红外器件材料,其材料体系的禁带宽度对红外区域可以有效覆盖,是制造红外探测器的理想材料,在医疗检疫、视频监控、导航夜视及特殊领域广泛应用,特别是在非接触式红外测温设备在检疫防疫中发挥了不可替代的作用。

以GaN、SiC为代表的第三代半导体材料,禁带宽度大、热导率高、电子饱和迁移速率高、击穿电场高,用其制作的器件相对于Si器件具有耐高压、低功耗、高频、小体积等优势:GaN微波射频器件在5G通信领域需求显著,也是下一代核心部件。GaN、SiC电力电子器件在以电动汽车、消费类电子、新能源、轨道交通等为代表的民用领域和以全电化舰船综合电力系统和特殊环境应用优势明显。目前第三代半导体材料及器件已经跨过了漫长的技术培育期,进入了快速的产业渗透及应用推广阶段。

以AlN、Ga2O3、金刚石等为代表的超宽禁带半导体材料,其高频特性、高温特性、功耗特性、耐压特性相对第三代半导体材料更为优越,是当前半导体技术研究的热点前沿。无论红外器件设备、第三代半导体设备还是超宽禁带半导体设备,其器件制造主要基于集成电路设备,工艺节点一般在微米量级,设备技术相对成熟。技术研究的重点主要在材料制备设备,以及针对具体材料特性对器件工艺设备的适应性改造方面。主要技术特征包括新材料制备所需的新方法,如金刚石制备MPCVD法;以及更大尺寸单晶制备所需的温场、流场控制等技术。

2 半导体工艺装备现状及发展趋势

2.1集成电路工艺设备

2.1.1 前道工艺设备

2.1.1.1 总体发展态势

集成电路前道工艺及对应设备主要分八大类,包括光刻(光刻机)、刻蚀(刻蚀机)、薄膜生长(PVD-物理气相沉积、CVD-化学气相沉积等薄膜设备)、扩散(扩散炉)、离子注入(离子注入机)、平坦化(CMP设备)、金属化(ECD设备)、湿法工艺(湿法工艺设备)等。

集成电路前道工艺及设备的标志性指标为集成电路的特征尺寸,主要沿摩尔定律方向持续延伸,根据国际器件与系统技术路线图IRDS(2021),集成电路前道关键工艺、器件结构对应的设备加工技术能力将由当前的5 nm、3 nm发展到2.1 nm、1.5 nm直至等效1 nm、0.7 nm技术节点,如表1所示。

表1集成电路逻辑器件技术路线图[1]

近期(2021-2025):FinFET晶体管结构继续延伸,由5 nm直至3 nm、2.1 nm节点。为进一步提升栅极控制能力,从3 nm节点开始, LGAA(Lateral gate-all-around,水平围栅)结构开始引入并逐渐替代FinFET结构,相应的制造设备应该随之进行技术迭代,支撑到这个制造节点的要求。

中期(2026-2030):晶体管全面进入2.1 nm以下节点,根据IRDS(2021)规划,2.1 nm和1.5 nm这两个工艺节点预计将分别在2025年和2028年出现。LGAA晶体管结构可以继续支撑这两个制造节点的要求,相关制造设备需要根据工艺特征尺寸缩小的要求做进一步提升。

远期(2031-2035):晶体管进入等效1 nm工艺节点和等效0.7 nm工艺节点,晶体管的工艺特征尺寸达到极限,多层垂直堆叠的LGAA晶体管结构将成为下一步发展方向。单片三维堆叠工艺及设备技术将是这个阶段的主要需求。

2.1.1.2 主要技术挑战

(1)EUV光刻设备。光刻技术直接决定了集成电路的特征尺寸(光刻线宽与光刻机曝光波长成正比,与成像系统数值孔径呈反比),是摩尔定律演进的核心驱动力之一。传统的193 nm光刻机在经历了“浸没式技术”及“多重曝光”两次重要技术升级后,已经大规模应用在10 nm节点集成电路制造中。进入7 nm以下节点,虽然193 nm浸没式光刻+多重曝光从技术上仍然可以满足集成电路制造的需求,但工艺复杂度直线上升,造成了难以解决的良率和成本问题。因此,采用13.5 nm极紫外光源的EUV光刻机成为7nm及以下集成电路大生产首要选择,在7 nm节点,EUV光刻工艺步骤是193 nm浸没式光刻的1/5,光刻次数是后者的1/3[4]。

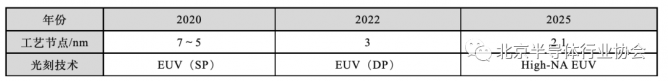

当前EUV光刻机已经在产线批量应用并支持7~5 nm节点的工艺制程要求。随着摩尔定律继续延伸,EUV光刻主要是按照两个方向演进:一是由单重曝光(Single Patterning, SP)发展至双重曝光(Double Patterning,DP);另一个就是提高EUV数值孔径(High-NA EUV)。根据IRDS光刻技术发展路线图预测,在3 nm节点(2022年),集成电路大生产将采用双重曝光EUV技术;在2.1 nm节点(2025年),集成电路大生产将采用高数值孔径EUV技术,如表2所示。

当前ASML正在研发第二代EUV光刻机,数值孔径将由现在的0.33提升至0.5,同时不断提升光源功率,预计量产时间为2024年,将支撑2025年之后集成电路制造的需求。

表2 光刻技术发展路线图

(2)GAA(围栅晶体管)制备设备。GAA(Gate-All-Around)晶体管将是继FinFET后的下一代晶体管结构。相对于FinFET的三面栅控结构,GAA晶体管沟道为水平或垂直纳米线,栅极四面环绕沟道,栅控能力更强,可以有效降低短沟道效应[5]。GAA结构预计于2022年3 nm节点开始导入集成电路大生产线,并于2025年2.1 nm节点成为主流器件结构。

GAA晶体管结构的引入和特征尺寸的进一步微缩,对集成电路制造工艺设备提出了更高的要求:离子注入机将更加强调共形掺杂(Comformal Doping)、薄膜和刻蚀工艺更加强调原子级的精度控制(ALD-原子层沉积、ALE-原子层刻蚀)、其他设备(如CMP、ECD、湿法工艺设备等)也需要做相应调整,以满足更高精度加工、非铜互联材料、新型HKMG材料等方面的需求。下面就共形掺杂设备、原子层刻蚀设备、原子层沉积设备做详细介绍。

共形掺杂的离子注入设备:晶体管采用三维结构以后,对共形掺杂(各向同性的掺杂,各个方向上均匀掺杂)的要求不断提升。传统的离子注入设备中,离子通过加速电场加速注入晶圆,掺杂的定向性强,为满足三维晶体管共形掺杂工艺的需求,离子注入设备有以下两个发展方向:(1)进一步提升离子注入机的束线角度、束线形状和注入剂量的控制能力,如应用材料公司的VIISta900 3D系统;(2)采用等离子体浸没式注入设备[6],在一层贴合晶圆表面结构的等离子体辅助下,实现各个方向的均匀掺杂,如应用材料公司的VIISta PLAD系统。

原子层沉积(Atomic layer deposition, 缩写ALD)和原子层刻蚀(Atomic layer etching, 缩写为ALE)[7]:进入纳米尺度以后,半导体制造对加工精度要求不断提高。以IMEC的堆叠纳米线GAA晶体管结构为例,制备过程为:在衬底上沉积多层SiGe/Si超晶格结构,完成Fin刻蚀后,通过选择性刻蚀去除SiGe,释放Si纳米线,然后沉积高K介质及金属栅(置换式金属栅工艺);在此过程中,SiGe结构刻蚀和纳米线的释放需要对实现对多层Si纳米线之间SiGe的横向精确去除,高K介质及金属栅的沉积需要在SiGe去除后的极小空间内完成,以上工艺均需通过ALE和ALD设备实现。ALE和ALD技术可以以一种自我限制且有序的方式在原子尺度逐层去除/沉积材料,赋予人们原子尺度的精细加工能力。

(3)设备智能化。集成电路技术在赋能信息技术产业的同时,新一代信息技术也在促进集成电路产业的发展,推动其不断迈向“智能制造”。集成电路制造设备智能程度不断提升,将逐渐具备晶圆状态追溯、先进工艺控制(缺陷监测、工艺过程控制)、设备能耗管理、预测性排产、预测性维护和虚拟量测等功能。要实现这些,除设备需要具有相应的信息采集及决策执行功能外,还需要产线信息系统的配合,单纯从设备的角度,根据IRDS预测,设备将按照表3所示的技术路线图发展,逐步支持智能化功能的实现。

表3 设备智能化技术路线图[1]

(4)450 mm(18英寸)设备。在一次工艺过程中,更大的晶圆尺寸可以生产更多的芯片,可以显著降低单颗芯片成本。晶圆尺寸不断增大是集成电路产业一直以来的发展趋势之一,由最初的100 mm (4英寸)、150 mm(6英寸),一直发展到今天的300 mm(12英寸,2001年引入,最早用于0.13 μm产线)。

2008年起,450 mm(18英寸)晶圆及其制造设备的生产被提上日程,初定于2012年组建18英寸试验产线,2015年开始大生产线替代。目前450 mm (18英寸)大硅片及450 mm(18英寸) 设备接口标准早已完成,但是由于450 mm(18英寸)设备研发及晶圆厂建线耗资巨大,450 mm(18英寸)晶圆设备的应用时间一再拖期。根据最新的IRDS技术路线图,450 mm(18英寸)设备的大生产线替代时间已经延后到了2025年之后。

2.1.2 后道工艺设备

2.1.2.1 总体发展态势

由于摩尔定律逐渐接近其物理极限,为进一步追求速度、功耗、功能与制造成本的平衡,后道封装更加强调封装集成度、I/O引脚密度及功能集成度,因此SiP、2.52D/3D集成及WLP成为未来集成电路后道封装工艺的发展重点。

当前最主要的封装形式仍然为倒装键合和引线键合,先进封装(包括2.5D集成、Fan-out WLP/PLP等)已经进入市场并占据一定市场份额,3D集成是当前技术研究热点。2018年底,英特尔发布了首个商用3D集成技术:FOVEROS混合封装。

传统的集成电路后道工艺设备主要包括:划切设备、减薄设备、键合设备、测试分选设备等。SiP、2.5D/3D集成、WLP等先进封装技术大量采用了前道工艺中的光刻、刻蚀、金属化、平坦化等工艺设备,集成电路前后道工艺呈现融合发展的态势。集成电路后道工艺设备的发展需要满足未来SiP、2.5D/3D集成、WLP等先进封装技术发展的需求。

2.1.2.2 主要技术挑战

(1)超薄晶圆减薄及划切设备。代工厂出厂的硅晶圆厚度一般为0.7~0.8 mm,为保证芯片小尺寸封装的要求,硅晶圆在封装中一般需要通过背面研磨/抛光过程进行减薄。当前大生产中引线键合芯片的减薄工艺可达30 μm,倒装芯片的减薄工艺一般在50 μm左右,晶圆减薄设备已经相对成熟,可以支持直到2030年的减薄工艺需求[3]。

超薄晶圆划切可能导致芯片的卷曲和碎裂,传统的机械划切和激光划切在划切质量和成本等方面都面临着极大的挑战。一种新兴的等离子体划切技术近年来逐渐受到关注:等离子体划切技术与干法刻蚀技术相近,利用等离子体物理轰击和化学反应在硅片表面形成深而细的沟槽,从而达到分割芯片的目的。相对于传统划切技术,等离子体划切具有三大优点:一是芯片侧壁无损伤,没有应力导致的芯片弯曲;二是可以实现多条线的批量划切,减少工艺时间;三是划切通道窄,减少材料损失。

(2)引线键合设备。目前,引线键合仍然是主流的芯片互联方式,占全部封装市场的77%左右,其中用于系统级封装的引线键合市场增长迅速。当前引线键合工艺及设备的发展趋势主要包括四个方面:一是降低成本(主要通过引线材料的变革,由Au线逐渐变更为Ag、Cu线);二是提高产能(近年来,除提升键合机定位平台电机速度外,键合工艺的优化在提升键合设备产能中发挥的作用越来越重要);三是互联密度更大(主要通过新的封装结构和工艺实现);四是采用智能引线键合机(智能引线键合机将实现精确的工艺控制、缺陷检测和可追溯性,从而缩短封装产品的研发时间、提高良率和产能,是未来先进引线键合技术发展的主要驱动力之一)。

(3)倒装键合设备。相对引线键合,倒装键合是高密度封装技术的主要发展方向,有助于实现堆叠芯片和三维封装工艺,在2.5D/3D集成、晶圆级封装、系统级封装等封装技术领域均有广泛应用。

目前倒装芯片的互联方式主要包括热超声(采用金球凸点,Gold stud)、回流焊(采用锡球凸点,Solder bump)和热压(采用铜柱凸点,Copper pillar)三种键合工艺。热超声倒装键合设备基于成熟的引线键合技术,主要用于I/O密度较低的芯片中;回流焊工艺设备通过热回流将蘸有助焊剂的芯片焊接在基板上,是相对主流的倒装焊设备;热压工艺设备主要面向铜柱凸点和微铜柱凸点,凸点密度更高,代表着倒装设备的发展方向,热压工艺设备最大的技术挑战是设备的装片精度(提高装片精度会牺牲工艺速度,从而增大工艺成本)。

除以上三种主要倒装键合技术外,正在开发的先进倒装技术包括基于热压工艺设备的无凸点Cu-Cu直接键合技术[8]。

(4)2.5D/3D集成。2.5D集成是传统的2D封装(两个裸片在封装体内水平排布)的升级,指两个或更多的裸片以倒装键合的形式在基板上水平排布。3D集成指两个或更多的裸片相互堆叠,并直接互联。2.5D/3D集成技术相对传统的2D封装,可实现更高的性能、更低的能耗、更低的延迟、以及更小的芯片尺寸。2.5D/3D集成都离不开TSV(硅通孔)、倒装键合等封装技术,TSV工艺是关键,相关设备发展是重点。TSV是通过芯片和芯片之间、晶圆和晶圆之间制造垂直通孔,在通孔中电镀铜实现垂直方向上芯片的互联,主要包括通孔刻蚀(使用深反应离子束刻蚀或激光打孔设备)、绝缘层/介电层沉积(CVD设备)、阻挡层/种子层沉积(PVD设备)、通孔镀Cu(ECD设备)、多余Cu去除(CMP设备)等工艺步骤,可见,TSV技术主要基于集成电路前道设备实现。

TSV工艺及设备技术在持续提升中,主要挑战和发展方向包括:高密度、高深宽比刻蚀、绝缘层和金属层的低温工艺、高速通孔填充、持续降低成本等[3]。

(5)晶圆级封装(WLP)。晶圆级封装是在晶圆上直接进行裸芯片封装,再切割形成独立的芯片。晶圆级封装可减少封装材料及工序,同时具有轻薄短小的特点,是封装技术发展方向之一。晶圆级封装作为一种新型封装形式,其制备过程同样需要基于键合、减薄、TSV等封装技术和设备。

晶圆级封装最主要的发展趋势是由晶圆级向板级发展:为了追求更高的生产效率进而降低成本,晶圆级封装从传统的以200 mm/300 mm晶圆形式封装向长方形板级封装发展,长方形基板尺寸从300 mm×300 mm、457 mm×610 mm、510 mm×515 mm提升至600 mm×600 mm。从设备角度来说,主要的挑战在于基板形状的变化,很多基于圆形基板的设备(如旋转涂胶设备)等,需要做适应性改造。目前韩国三星电机(SEMCO)和纳沛斯(Nepes)公司都在开展板级封装设备的研发[3]。

2.2 分立器件相关制造设备

2.2.1 第三代半导体设备

第三代半导体设备主要为SiC、GaN材料生长、外延所需的特种设备,如SiC PVT单晶生长炉、CVD外延设备以及GaN HVPE单晶生长炉、MOCVD外延设备等;以及SiC器件制备中所需的高温设备(高温离子注入机、高温退火炉、高温氧化炉等);其他部分设备也需针对第三代半导体工艺做定制性开发。

第三代半导体设备的发展主要面向晶圆尺寸逐渐增大的需求。SiC材料及器件装备方面,150 mm(6英寸)已经成为国际主流,200 mm(8英寸)逐渐转入商用;GaN材料及器件装备方面,SiC基GaN装备正在由100 mm(4英寸)向150 mm(6英寸)过渡;Si基GaN装备正在由150 mm(6英寸)向200 mm(8英寸)过渡;GaN自支撑衬底所需的HVPE设备已经可以满足50~150 mm (2~6英寸)GaN衬底的制备需求。

2.2.2 红外焦平面探测器制备设备

当今红外焦平面探测器已经发展到第三代,主要以HgCdTe(碲镉汞)、InAs/GaSb II类超晶格材料为代表。红外焦平面探测器设备主要为HgCdTe、InAs/GaSb(砷化铟/锑化镓)材料生长、外延所需的特种设备如HgCdTe液相外延(LPE)设备、分子束外延(MBE)设备等,其他部分设备需针对红外焦平面器件工艺做定制性开发。

红外焦平面探测器设备的发展主要面向解决器件小间距、超大面阵、多谱段方向发展的工艺需求,器件面阵大小将由当前的2.7K2.7K,逐渐向4K4K、8K8K、30K30K发展。包括大视场特种投影光刻、高压碲化汞单晶炉、高平整度晶片加工等一批关键工艺设备。

2.2.3 新兴材料及制备设备

当前,以氮化铝(AlN)、金刚石、氧化镓(Ga2O3)等为代表的超宽禁带半导体材料日益成为研究热点,主要处于材料制备技术研发、性能优化及器件应用探索阶段。超宽禁带半导体专用设备主要为相关材料制备所需的晶体生长、薄膜外延设备。

AlN制备设备。主要包括用于晶体生长的PVT设备和用于薄膜外延的高温MOCVD设备等。PVT设备方面,已实现50 mm(2英寸)AlN单晶产业化;高温MOCVD设备方面,已经可以支撑50~100 mm(2~4英寸)衬底的高温外延生长需求。

金刚石制备设备。半导体级金刚石单晶制备主要通过CVD法实现,可选的制备手段包括微波等离子体化学气相沉积(MPCVD)法、等离子体喷射CVD法、热丝化学气相沉积(HFCVD)法、热阴极等离子体CVD法、激光诱导等离子体CVD法等。其中MPCVD法是目前制备高品质金刚石薄膜的首选,主要技术挑战是大尺寸金刚石薄膜的制备。

氧化镓制备设备。氧化镓单晶制备可通过以下方法实现:焰熔法、光学浮区法(OFZ法)、边缘限制薄膜生长法(EFG法)、垂直梯度凝固法(VGF法)、垂直布里奇曼法(VB法)和直拉法,其中EFG法和直拉法获得的单晶质量最高,是最有前途的半导体级氧化镓单晶制备技术。目前通过直拉法最高可获得50 mm(2英寸)的氧化镓单晶、通过EFG法可获得100 mm(4英寸)的氧化镓单晶,150 mm(6英寸)EFG法单晶工艺及设备正在开发中。氧化镓外延设备主要包括MOCVD、MBE、HVPE等,其中MOCVD、MBE是器件制备中最常用的两种设备。

3 结束语

自1947年晶体管问世以来,半导体技术已经走过70余年风风雨雨,衍生出集成电路与微系统、光电子分立器件(激光器、探测器等)、微电子分立器件(微波射频器件、电力电子器件)等诸多细分领域。集成电路主要沿摩尔定律和超越摩尔定律两个方向发展,其工艺装备引领了整个电子制造产业的工艺节点演进;分立器件发展主要通过基础材料创新实现,其工艺装备在集成电路工艺装备的基础上,主要着眼于特定材料体系生长和加工的需求。总而言之,半导体工艺及制造装备技术的进步主要由特征尺寸(CD)的减小、新器件结构和新材料等因素驱动,以原子级的加工能力、丰富的集成形式、支持多种新材料体系为特征,现代半导体工艺及制造装备技术将持续支撑整个电子信息产业的技术创新需要。

信息来源:《电子工业专用设备》2022年第4期“趋势与展望”)

作者:周 哲1,付丙磊2,董天波1,芦 刚3

(1. 中电科电子装备集团有限公司,北京 100070;2. 紫光国芯微电子股份有限公司,北京 100083;3. 中国电子科技集团公司第四十五研究所,北京 100176)