传统集成电路技术使用平面展开的电子型和空穴型晶体管形成互补结构,从而获得高性能计算能力。其密度的提高主要通过缩小单元晶体管的尺寸来实现。例如7nm节点以下业界使用极紫外光刻技术实现高精度尺寸微缩。极紫外光刻设备复杂,在现有技术节点下能够大幅提升集成密度的三维叠层互补晶体管(CFET) 技术价值凸显。然而,全硅基CFET的工艺复杂度高且性能在复杂工艺环境下退化严重。因此,研发与我国主流技术高度兼容的CFET器件与集成,对于自主发展新型集成电路技术具有重要意义。

针对这一关键技术,复旦大学微电子学院周鹏教授、包文中研究员及信息科学与工程学院万景研究员创新地提出了硅基二维异质集成叠层晶体管。该技术利用成熟的后端工艺将新型二维材料集成在硅基芯片上,并利用两者高度匹配的物理特性,成功实现4英寸大规模三维异质集成互补场效应晶体管。在相同的工艺节点下实现了器件集成密度翻倍,并获得了卓越的电学性能。北京时间2022年12月9日,相关成果以《硅和二硫化钼异质互补场效应晶体管》(Heterogeneous Complementary Field-effect Transistors based on Silicon and Molybdenum Disulfide)为题发表于国际顶尖期刊《自然-电子学》(Nature Electronics),文章链接:https://www.nature.com/articles/s41928-022-00881-0。

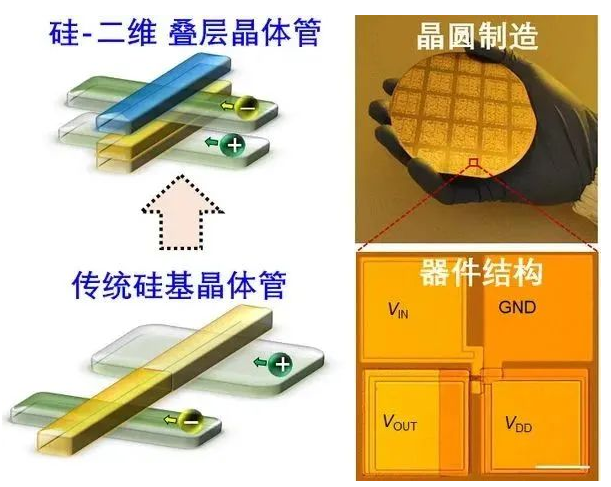

复旦大学研究团队将新型二维原子晶体引入传统的硅基芯片制造流程,实现了晶圆级异质CFET技术。相比于硅材料,二维原子晶体的单原子层厚度使其在小尺寸器件中具有优越的短沟道控制能力。

图:硅基二维叠层晶体管的概念、晶圆级制造与器件结构

研究团队利用硅基集成电路的标准后端工艺,将二硫化钼(MoS2)三维堆叠在传统的硅基芯片上,形成p型硅-n型二硫化钼的异质互补CFET结构。二硫化钼的低温工艺与当前硅基集成电路的后端工艺流程高度兼容,大幅降低了工艺难度且避免了器件的退化。同时,两种材料的载流子迁移率接近,器件性能完美匹配,使异质CFET的性能优于传统硅基及其他材料。例如其反相器增益在3V供电时高达142.3V/V,在超低压供电0.1V时其增益达1.2V/V且功耗低至64pW。团队还验证了该新型器件在 “全在一”光电探测及气体传感中的应用。

目前,基于工业化产线的更大尺寸晶圆级异质CFET技术正在研发中。该技术将进一步提升芯片的集成密度,满足高算力处理器,高密度存储器及人工智能等应用的发展需求,助力打破国外在大规模集成电路领域的技术封锁。

相关工作得到了科技部重点研发计划、国家自然基金委杰出青年基金、上海市探索者计划等项目的资助,以及教育部创新平台的支持。

(来源:复旦大学微电子学院)