传统SiC功率模块封装仍以铝线键合互连为首选互连技术,然而铝线键合的寄生电感大(大于10 nH),开关损耗高,热失配引起的应力失效率高,这些都极大地限制了SiC功率器件的性能和可靠性。对于多芯片并联的SiC超级结器件来说,开发多层平面互连的高密度集成化封装技术是提高其性能和可靠性的必然途径。随着高密度集成化封装的发展,其电-热-磁-应力可靠性等技术难题也显得愈发突出。为了保证功率器件的性能和可靠性,需要研究高密度集成封装的多物理场耦合作用规律和优化方法。

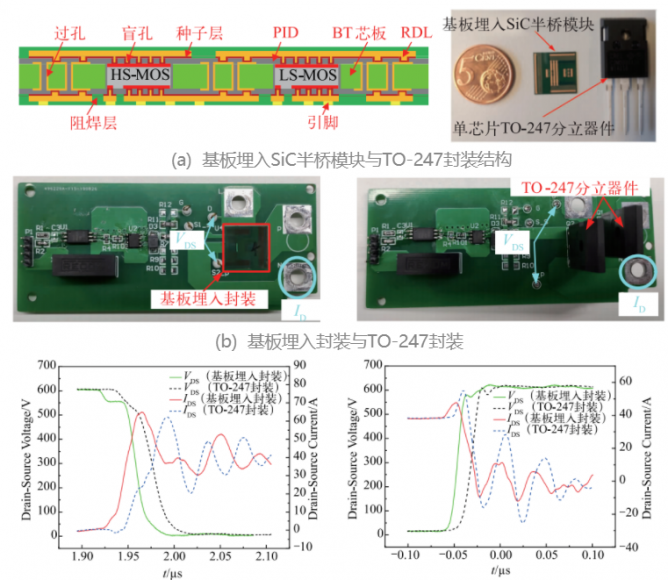

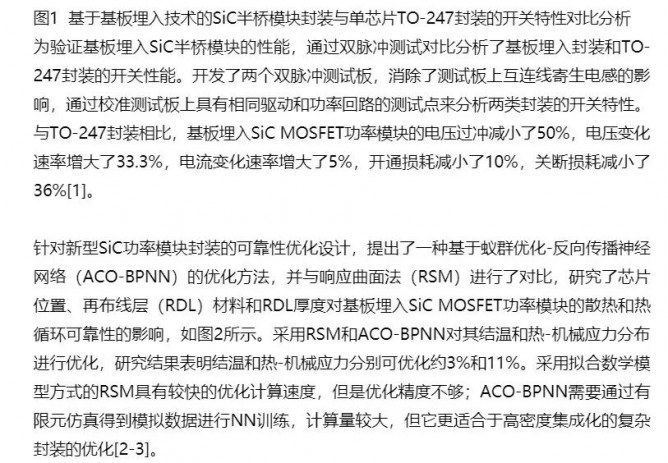

中科院微电子所侯峰泽副研究员和复旦大学樊嘉杰青年研究员提出了一种基于基板埋入技术的新型SiC功率模块封装及可靠性优化设计方法:采用新型光敏成型介质(PID),通过光刻工艺制备SiC MOSFET功率器件电极上的互连盲孔;基于板级物理气相沉积(PLPVD)技术批量更改SiC MOSFET等功率器件电极上的金属;通过双面再布线层(DSRDL)工艺替代功率器件的传统键合技术。开发的新型有机基板埋入SiC MOSFET半桥功率模块样品厚度薄,体积远小于传统TO-247封装(如图1所示)。

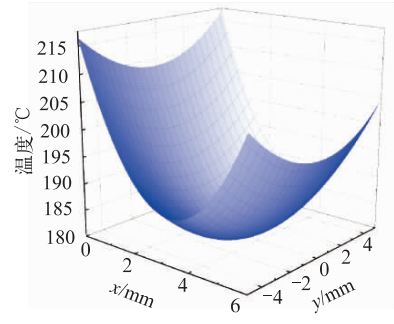

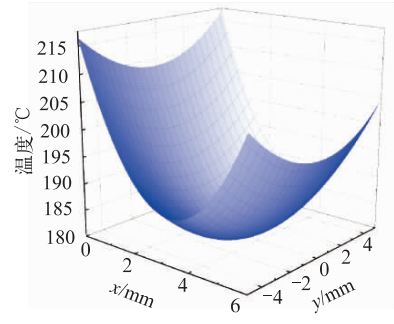

(a) 模拟芯片散热情况

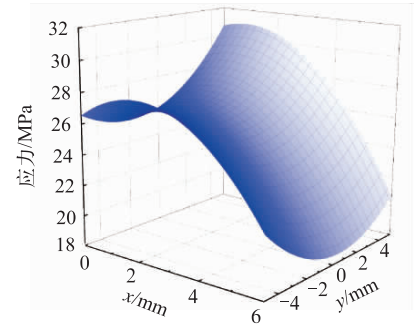

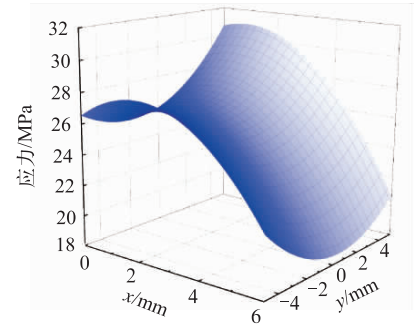

(b) RDL中的应力分布模拟

(c) 温度等高线

(d) 应力等高线

(d) 应力等高线

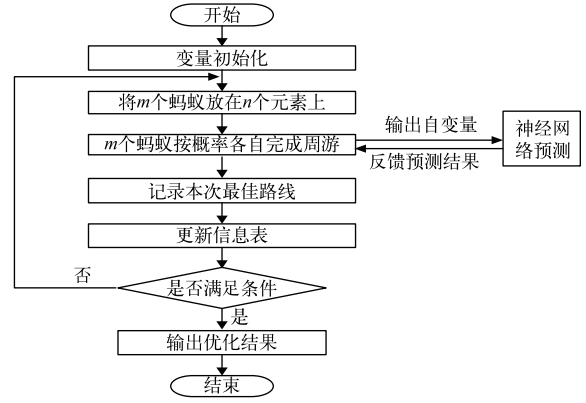

(e) ACO-BPNN流程图

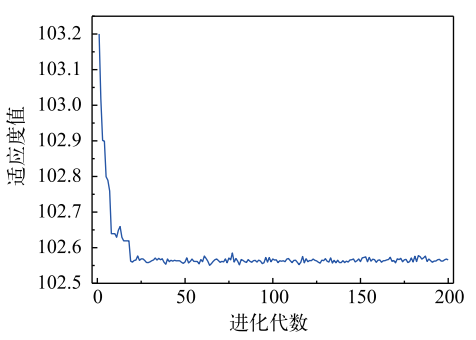

(f) 适应度曲线

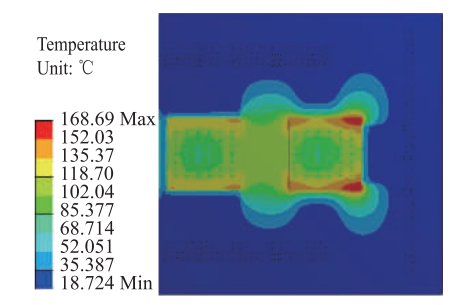

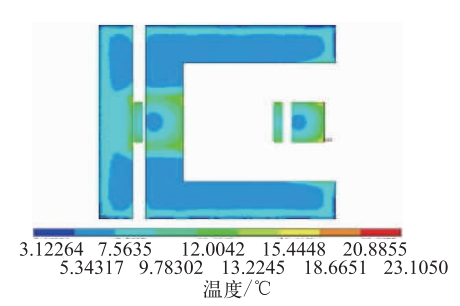

图2 基于蚁群优化-反向传播神经网络算法的基板埋入式SiC功率模块封装可靠性优化

原文文献:

[1]HOU F Z, WANG W B, MA R, et al. Fan-out panel-level PCB embedded SiC power MOSFETs packaging[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 367-380.

[2]QIAN Y C, HOU F Z, FAN J J, et al. Design of a fan-out panel-level SiC MOSFET power module using ant colony optimization-back propagation neural network[J]. IEEE Transactions on Electron Devices, 2021, 68(7): 2021.

[3]樊嘉杰,钱弈晨. 一种高可靠性的嵌入式SiC功率器件封装设计方法:ZL202110700564.6[P]. 2022-04-01.

来源:电子与封装