对于任何半导体来说,封装对于电气隔离、产品稳健性和热管理都很重要。尤其是对于功率半导体来说,这是至关重要的。

随着向碳化硅 (SiC) 和氮化镓 (GaN) 等宽带隙 (WBG) 材料的转变,这些材料实现的更高电流密度和开关速度带来了更严格的封装要求。

在处理 GaN 时,与硅 (Si) 相比,还有两个额外的考虑因素可以优化器件性能。

通过 GaN/AlGaN 异质结界面处的二维电子气 (2DEG) 通道实现 GaN 的快速切换潜力。

GaN的导热性比较差。(在 300 K 时约为 1.3 W/cm.K,而硅的 1.49 W/cm.K 和碳化硅的 3.7 W/cm.K)

假设体热导率并不明显低于硅,但请记住更高的电流密度——它仅限于异质结周围的一个小区域。

尽管并不理想,但传统的 Si 封装可以并且已经用于封装 GaN 等 WBG 器件。TO-247 封装通常用于硅 (Si) 功率 MOSFET 和 IGBT,其中die底部(即漏极或集电极触点)直接接合到铜引线框架。在应用中使用时,标准做法是使用通孔开口将其直接安装到散热器上。

这个想法相当好地转移到了 SiC MOSFET,它们与 Si 对应物具有相似的结构。然而,今天的 GaN 器件采用横向设计,结构仅限于芯片顶部。这意味着失去了大部分冷却效益。横向 GaN 结构带来的另一个挑战是布局相关。所有三个器件端子(栅极、源极和漏极)都需要焊盘和相关的键合线以某种方式安装在芯片周围。

使用 GaN 的一个主要卖点是能够缩小产品尺寸。因此,对于分立 TO-247 封装中的 Si 功率 FET,相同的电压和电流额定 GaN 对应物可以封装在表面贴装 QFN 型封装中。

不幸的是,从热管理的角度来看,这使得事情更具挑战性。请记住,更高的电流密度将需要更严格的封装解决方案——QFN 中更小的芯片需要更多的热管理而不是更少。今天,一些制造商已经开始调整这些封装以适应他们的应用。

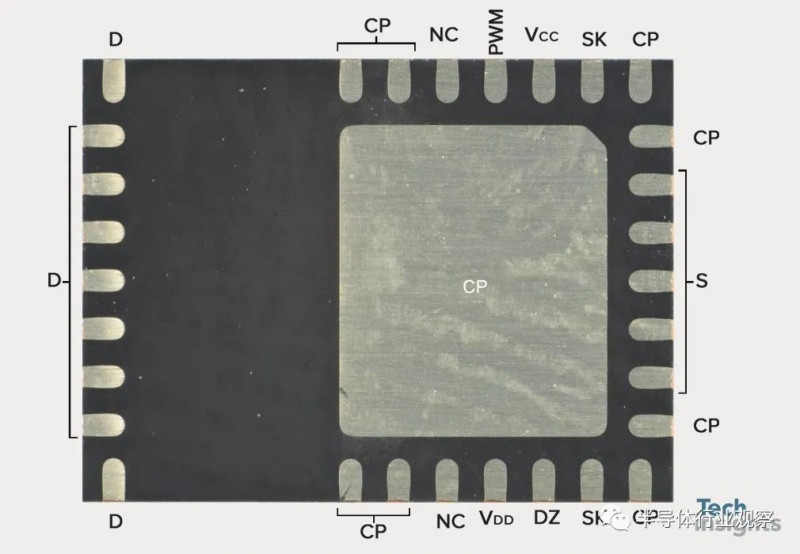

例如,参见 Navitas NV6128,这是一款单片集成 GaN IC,适合 QFN 封装的多个输出端口。如下图所示,可以看到带有端口注释的封装底部。GaN die位于冷却垫“CP”顶部的一侧。这对于这个设备来说显然已经足够了;尽管有趣的是,对于Navitas 最近宣布的带有“GaN Sense”的第三代 GaN,他们将重点放在了用于检测和控制工作温度的控制电路上。

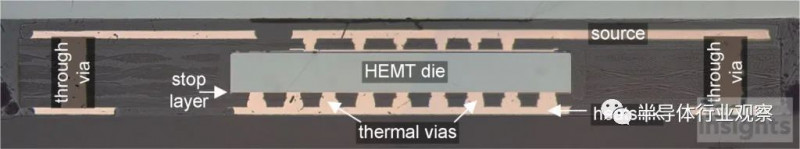

其他制造商已开始关注 GaN 特定封装解决方案。例如,GaN Systems 有几个封装,其中嵌入了芯片。如下图中的 GS61008P 横截面图。铜柱通过封装通孔直接连接到管芯的顶部和底部,然后将它们连接到散热器。

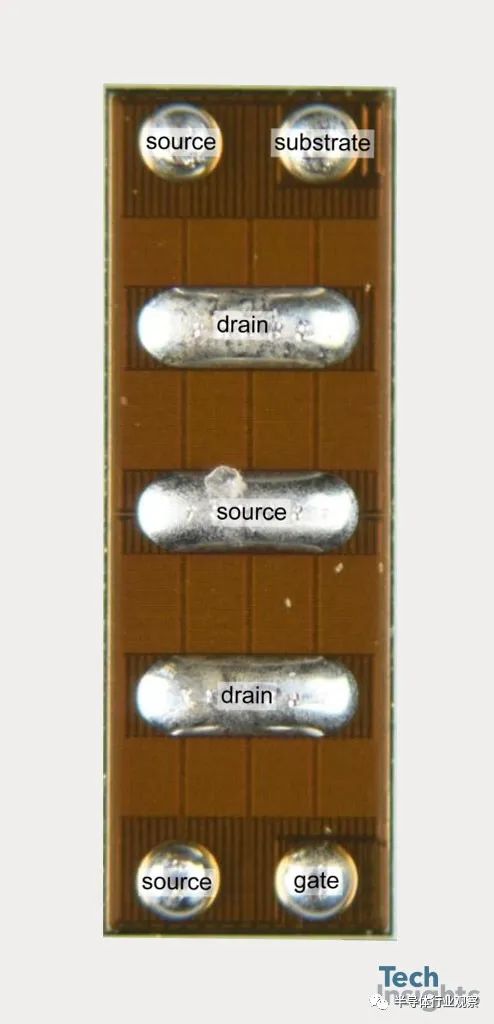

GaN 的另一个考虑因素是什么——优化开关性能?最小化封装寄生元件是实现这一目标的关键。EPC采用基本无封装或“晶圆级”封装的激进方法。这本质上只是一个带有焊料凸块/焊条的钝化芯片,用于直接连接到 PC(参见下图)。由于缺少相关的键合线,寄生电感被最小化,接口的热阻源也被最小化,因为理论上芯片本身可以直接键合到散热器。然而,电路设计人员在芯片贴装时需要注意和可能的特殊条件。EPC 最近打破了这一传统,推出了一款封装器件 EPC2302. 这种顶部暴露的情况似乎是晶圆规模和嵌入式芯片之间的某种折衷方案。

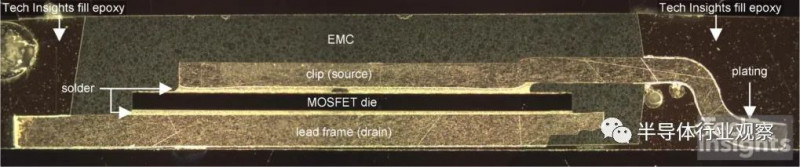

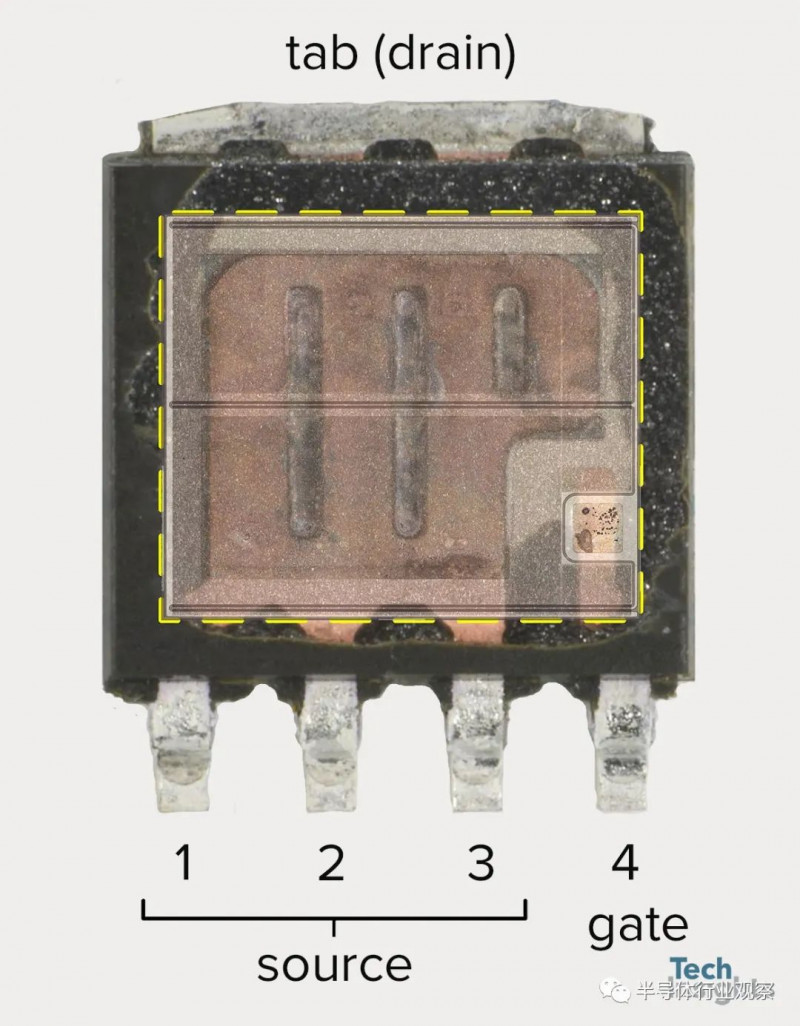

另一种降低电感的方法来自 Nexperia 的“铜夹”设计。他们最小化寄生电感的想法再次是通过移除键合线。如下图中 PSMN3R9 Si MOSFET 的横截面(请注意,该封装也已应用于 GaN 器件)。

下图显示了该设备的平面图,它已被喷射蚀刻以暴露铜夹。这直接焊接到芯片的源极触点。

总结

尽管 GaN 等宽带隙器件的定制封装仍处于起步阶段,但它是一个将在未来十年内得到大力发展的主题。有创新的解决方案可以转移器件端子,例如焊盘下电路 (CUP) 结构和穿 GaN 沟槽开始进入市场。

目前正在进行关于更好的热界面材料和芯片连接方法的学术研究。从传统的焊接转向使用银的烧结方法正在获得动力。

GaN 尚未在高功率模块设计中找到立足点,但在尖端的 SiC 模块中,我们开始看到特殊的陶瓷基板(如 Si 3 N 4和 AlN)用于出色的散热。

Die本身有解决方案吗?Power Integrations 采用的是使用蓝宝石衬底上的氮化镓晶圆而不是硅衬底上的氮化镓的方法,而学术研究则研究了更奇特的方法,例如在金刚石上生长的 GaN。