所谓的后摩尔时代,就是根据1965年摩尔提出来的当成本不变的情况下,性能和密度都要增加1倍。在这个基础上,他说每年增加1倍,十年以后,他说每年增加1倍的话,根本就没有赚钱的机会,十年以后,1975年就改成两年一次新技术的诞生,这样的话就可以可持续支持研发持续发展。到2005年,他说摩尔定律由于成本的问题恐怕很难走下去。后来他在两个会议上提出,技术走到2025年,他觉得走不下去了。所以摩尔定律的发展经过50、60年的历程,走得相当远了。

我们来看看现在把它定义为一个后摩尔时代,我个人觉得如果从摩尔当时的定义,从这两条曲线可以看到,红色的是英特尔的,另外一条是台积电的,我们可以看到从22纳米一路走过来,走到当今英特尔的10纳米,与台积电的7到5个纳米,我们可以看出来,在一个平方毫米上的晶体管的数量达到1个亿左右,如果走到7纳米、5纳米就可以到1.7个亿每平方毫米,有1.7亿的晶体管在里面。这说明什么问题呢?说明原来摩尔说的,每两年晶体管的密度要翻一番,在这里显然是做不到的,我们看到两家龙头企业做不到,所以基本上放弃每两年晶体管密度加1倍的提法。所以我个人觉得,这是一个后摩尔时代的重要标志。

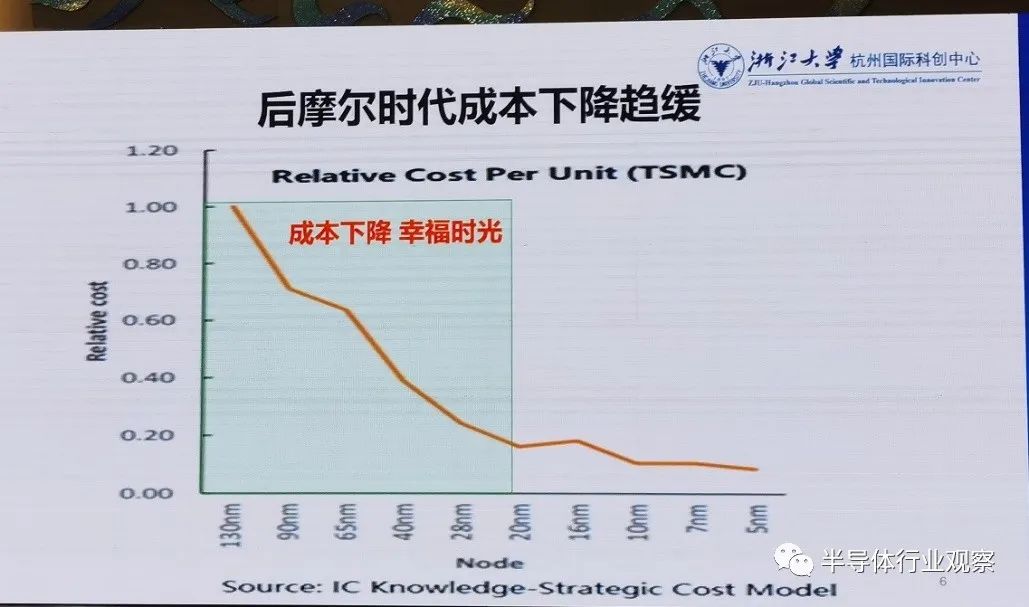

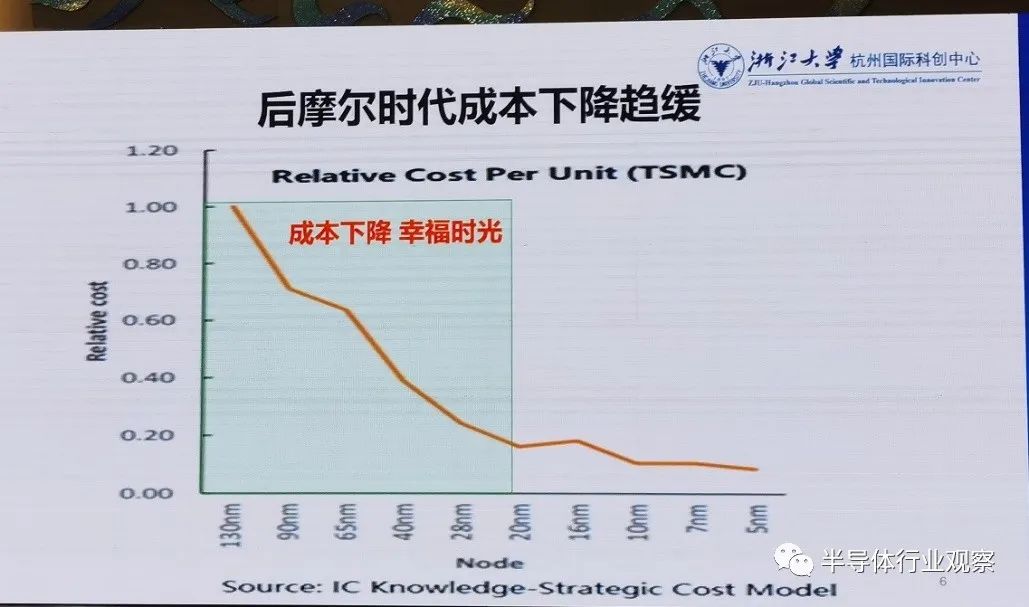

另外一个标志,就是制造成本,我们把台积电的数据拿出来看看,我们可以看到在0.13微米到28纳米这个区间,成本的下降是非常厉害的,基本上可以跟随摩尔定律的节奏。但是降到28纳米以后,进入20纳米节点的时候,我们可以看到制造成本的下降就非常艰难了,完全做不到成本下降了,质量不变。所以我觉得这两个应该是后摩尔时代的特征。

后摩尔时代的挑战和机遇是什么呢?我跟大家分享一下,下面是一张网上下载的图,从这张图我们可以看到集成电路的性能提升,从1978年X轴的最左边一直延伸到,这个数据是2018年,我们可以看到在2002年以前,晶体管、集成电路的性能每年提升52%,后来每年可以提升23%,到2010年以后,每年提升12%,但是到2014年以后,我们的性能提升就只有3.5%,所以每年的性能提升已经达到一个饱和的状态,再也不能像以前这样性能提升1倍,就很难持续下去。这是从技术层面来看它应该也是一个后摩尔时代的标志。

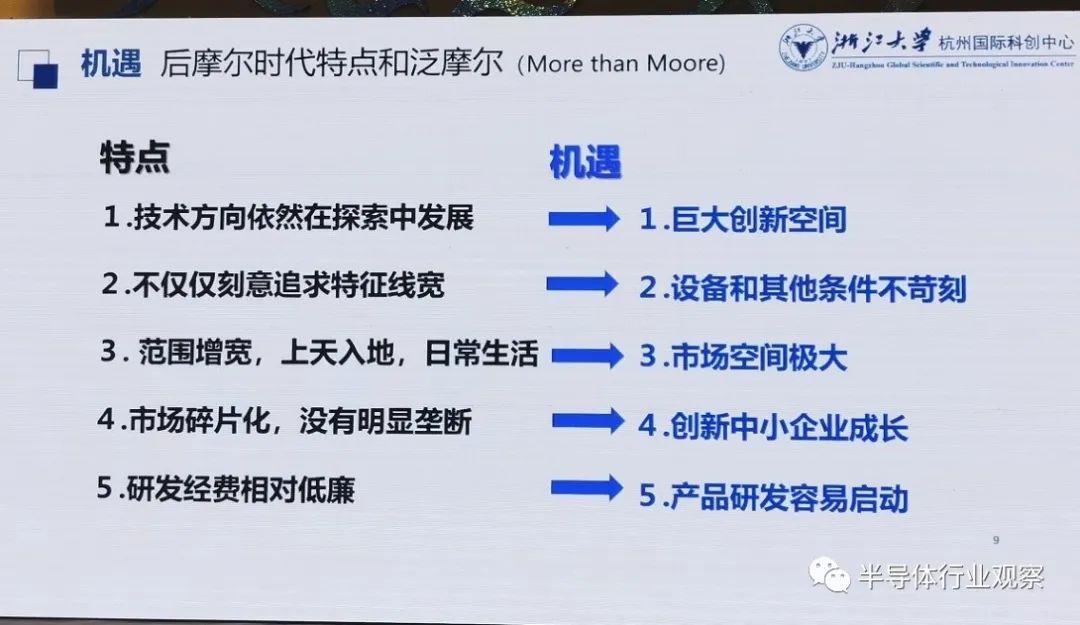

那么在后摩尔时代带来一些挑战,有它的一些特点,大家比较看好的技术会走得比较泛宽一点,我个人觉得是叫泛摩尔定律,在后摩尔时代要走的技术基本上呈现了一下几个特点:

1、技术方向很不清楚,各走各有的途径,八仙过海,各显神通;

2、大家放弃了对一个特征线条单一参数的追求,不用去追求一个单一的特征;

3、应用场景更宽,因为从现在无论是大数据、5G通讯等等,它的应用是上天入地,日常生活不所不在;

4、市场碎片化,没有一个明显的垄断,比如说我们来一个可穿戴的产品,比如智能手表,就很难说哪个是最垄断的,没有,因为各有各的特点,各有各的功能,各有各的需求;

5、研发经费相对来说低廉,因为你如果不去追求单一特征尺寸的话,不会动辄几个亿,多则几十个亿的美金要投进去,不是这样的,因为后摩尔时代一些小众的产品在市场上挺有生存空间的。

机遇就是:

1、既然技术发展方向不那么明确,创新的空间很大;

2、设备和其他条件没有那么苛刻。

3、市场空间很大;

4、对中小企业的成长很有利;

5、产品研发起来比较容易启动。

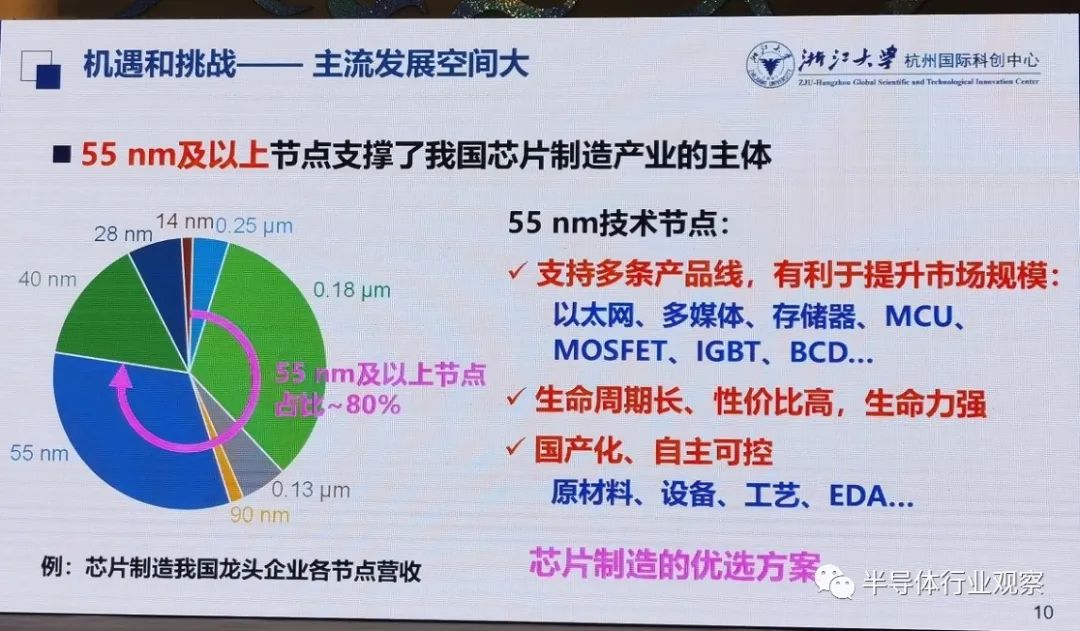

下面这张图是后摩尔时代国内一家龙头企业的财报,我们可以看出来,它整个收入的支撑点还是在55纳米为基础的,真正在高端上的支撑点还是非常小的比例。也就是说一些相对成熟的工艺,它的占比大概是80%,也就是说我们做一些相对成熟的工艺,其实有很大的市场和创新空间。

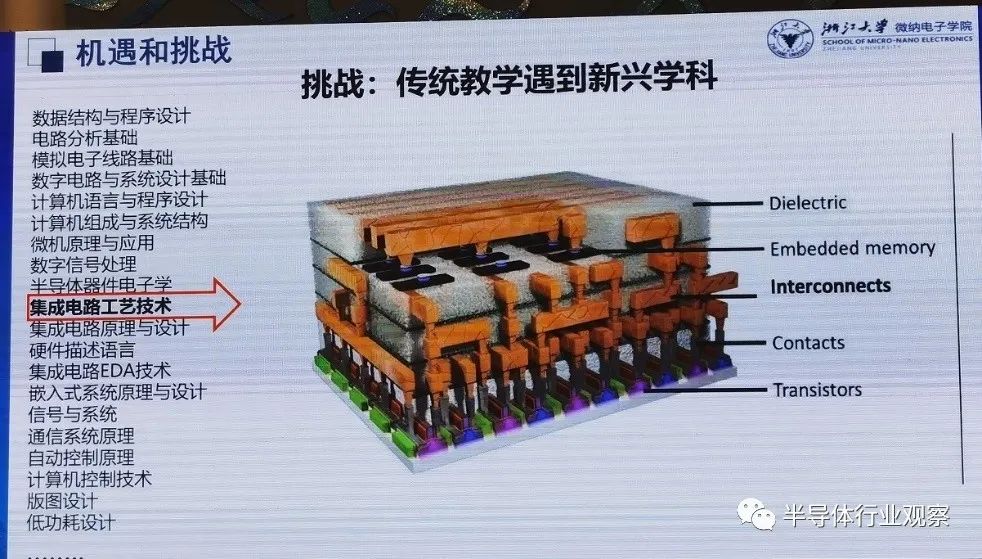

在整个制造中间,我自己本人也是最近两年才到教育系统,到浙江大学从事教育工作,我前面的时间都是在企业里或者在研究所,从事一些研究、技术开发工作。到大学以后,我就把浙江大学的微电子学院的讲义和教材翻出来看了一下,其实这个讲义和教材,北大、清华一些微电子的教材都是大同小异,差不多都是这个样子,反正有几十门课。但是你仔细一看,里面的教材90%以上都是讲设计的。刚才少军介绍说我们国家的产业发展最短的短板还是在制造上,但是从我们国家教育系统来看,也就是不到10%的教材是在讲制造方面的事情,基本上我们的微电子学院都是讲设计,讲制造非常少。

但实际上这个短板里面的核心是什么?就是集成电路的工艺,就是要把这个晶体管做到硅里面去,下面这张示意图的最下层是由成千上万个晶体管,通过各种各样的导体,把它连出来,再通过很长的铜线把晶体管连接起来,就形成了这样一个集成电路芯片的基本结构。

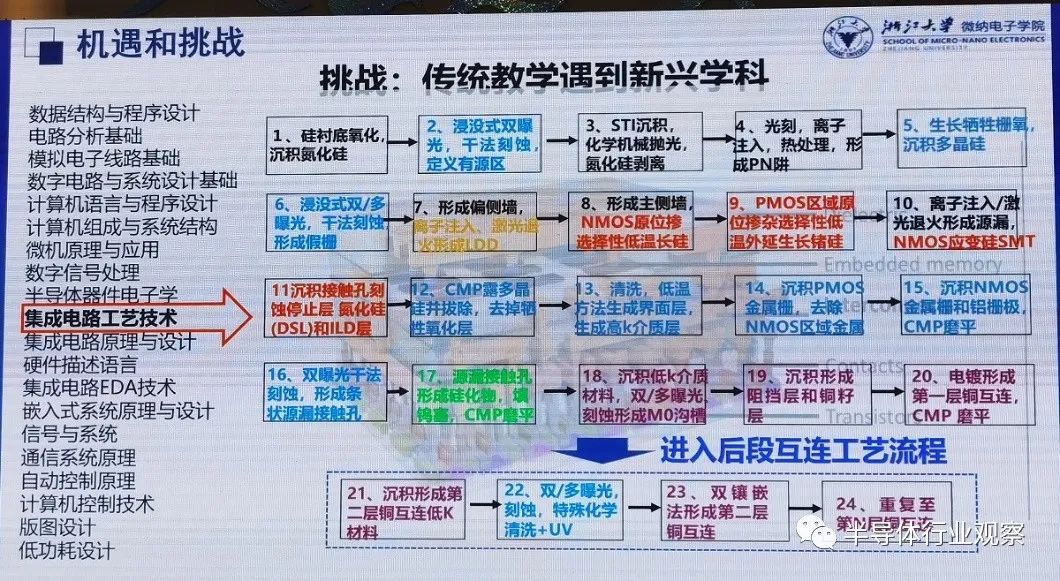

在制造过程中间,流程非常长。举个例子,如果做28纳米的制造,它的工艺流程非常长,整个流程大概有1000多步,其中最复杂的、最具挑战的大概是前段工艺,它的工艺流程大概有一半是前段工艺的一些技术。我们可以看到,所谓的前端工艺就是要把晶体管做出来。晶体管做完以后,我们就要把这些晶体管连接起来,形成所谓的后段工艺,就是把晶体管连接的工艺,从130纳米以后这个连接技术就是由铜来连接,而不是由铝。在连接里面,虽然它的花样,它的种类没有那么多,基本上就是薄膜、光刻来回做,因为取决于铜有多少层的固定层,通常现在的都是10多层,就反复做。所以整个来看,后段的工艺所涉及到的学科基本上以材料科学为主,前段工艺在晶体管制作中间实际上就是固体物理的东西,这两段对于学科的要求是不一样的。

刚才很长的工艺流程中间,我们拿出来三个工艺模块,我们可以看到,做图形的那一部分,就是光刻和刻蚀上面,我们所涉及到它的物理学,包括里面的光学、等离子体、表面物理等等,还涉及到数学、化学、材料、精细化工等等很多学科都会卷进来。做薄膜工艺的时候所涉及到的也有很多学科,包括摩擦学都会进来,因为在CNP里头有相当多摩擦学的基本概念在里头。像阱的制备,加速器物理等等都会涉及进来。所以整个交叉学科在工艺里面的体现是非常明显的,集中体现了交叉学科的体征。

从这里我要强调一下,我们做芯片制造,其实最大的特点就是要有成套工艺,而不是某一段工艺,刚才我说的1000步工艺,并不是说其中几步工艺,所以我觉得成套工艺是我们芯片制造的核心的核心,也是我们产业水平的标准。所谓成套工艺就是我们首先要工艺流程设计,关键的工艺设备的验证,关键工艺模块的开发,最后把模块里面的工艺参数的优化,优化以后最重要的一步把它成套集成起来,就形成一个天衣无缝的组合,就做成一个我们需要的芯片。

整个这个流程过程中间,我们可以看到,像产业里面的一些终极目标就是它的良率提升,不管你是新企业、老企业、大企业、小企业永恒的目标和挑战,就是良率提升技术,这就相当于一个产业的共性技术。

下面是我前几天画的一张图,我想表明这样一个意思,我们在集成电路芯片制造里面有很多学科,从数学、物理、化学、化工、计算机等等很多学科,但是这些零零散散分布在理工科高校里面的这么多学科,只有通过一个成套工艺的集成这么一个载体,才能把它形成一个产品,产生它的价值。正是通过成套工艺,我们形成产品的过程中可以关注一些产业的共性技术,比如工艺集成的优化、良率提升,包括现在想做的虚拟制造等等,像这些工艺技术缺少了成套工艺是没有结果的。

所以,现在我们看到国内有很多平台,都说对产业的共性技术进行研究,但是个人觉得,脱离了成套工艺,对产业技术所谓的共性研究是很难的,必须依托成套工艺,才能在制造的共性技术上有所支撑。

我举个例子,作为交叉学科,我们在用等离子体物理的基本概念用一些刻蚀的,比如我刚才提到的,我们需要用铜,铜不能刻蚀,它是非挥发性的,是惰性非常好的材料,一般的刻蚀没法惊醒。于是我们想起我们老祖宗景泰蓝的办法,在陶瓷上拉个图形出来,把铜嵌入进去,最后用沙皮打一打,就是我们景泰蓝,我们有上千年的历史,很遗憾那个时候我们没有形成专利。IBM大概在30年前,把制造铜,只能是在介质里面,挖了沟以后,把铜填进去。在这个体系里面,我举个例子,比如说我们等离子体物理的基本概念怎么用起来呢?我们看在铜的连接线里面,我们通常会打个通孔,把通孔的BUG填进去,最后把沟槽蚀刻,最后再把铜填进去,通过这样的流程把后面的铜通点做出来。

在整个流程中间,我们通过等离子体的刻蚀,把这个通孔做出来的时候,就需要通孔在刻蚀的过程中,在底部形成的曲面是凸形的,而不是凹形的,这样的话可以提升良率。于是我们希望等离子刻蚀的时候,希望这个离子进入通孔以后是发散的,使得离子轨道发生变化了,只能增加表面电荷。我们通过一些等离子体物理的特征,把它表面电荷增强以后,形成了右下角的图形刻蚀的剖面。这个技术土地通过有物理背景,通过等离子物理的运用,于是我们想到等离子可以控制地层的剖面,控制剖面的时候,现在最流行的我们知道双曝光,在这个过程中是不是可以利用等离子体对刻蚀表面控制的特征,目前形成这个过程的途径很多,我们觉得也许通过等离子物理的基本概念运用,可以得到这个过程。

举这个例子,就是给大家演示,一些学科在成套工艺流程中间,有很多发明点,很多创新点。

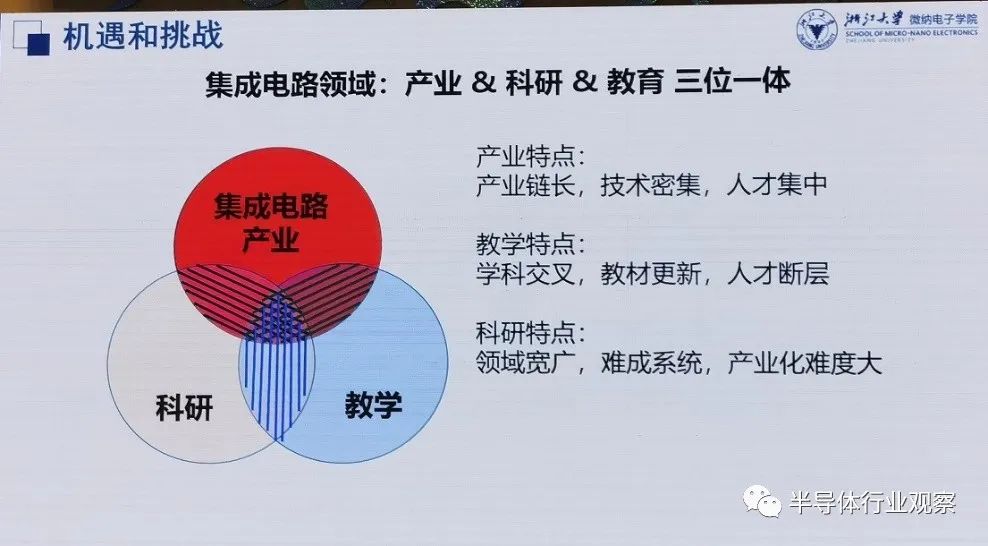

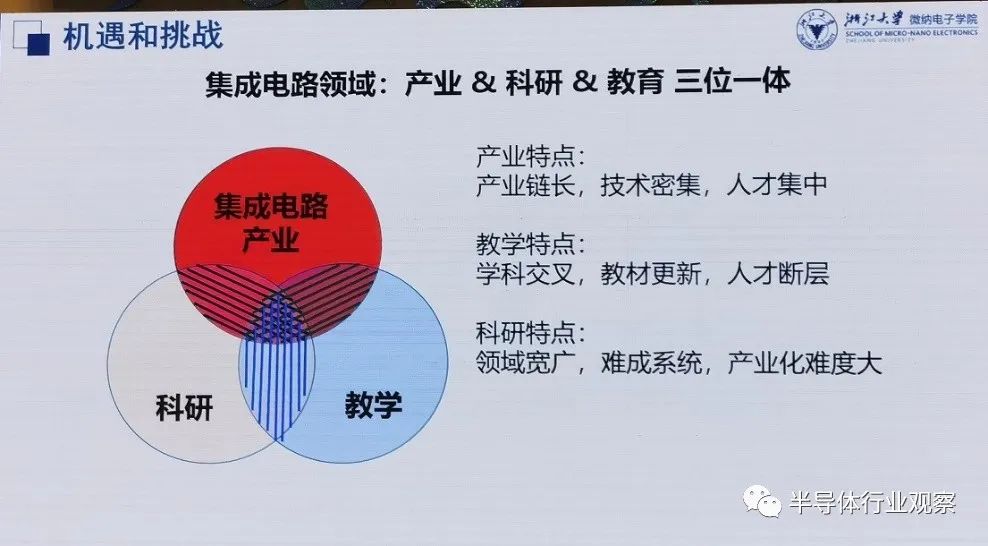

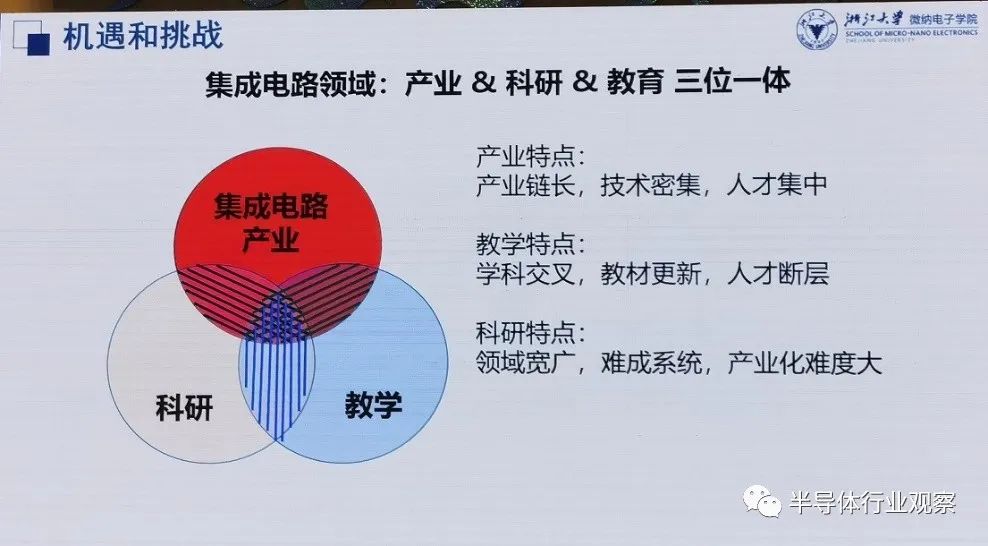

既然整个工艺流程那么复杂,通过一个企业或者一个单位来做是不现实的,所以我们必须通过国内顶尖的企业,顶尖的高校,顶尖的研究所,我们一起来做这个集成电路产学研三位一体的发展,就是产学研。比如说必须要加强集成电路产业和科研的关系,以及科研和教学的关系,教学和集成电路产业的关系。因为这个产业呈现了三大特点,第一个是产业链特别长,不是某一个专业可以涵盖的;第二个,从教学上来看,因为它的学科太交叉,不是一个系、一个学院搞得定的,通常是一个理工科大学里面很多行业都可以卷进去;第三个,科研特点,它的领域特别宽,产业化的难度非常大,尽管我们看到很多核心技术突破,真正对产业支撑的少之又少。

既然这么难做?我们产学研的合作,尤其是譬如科研跟产业的合作这一块有个共同区,教学跟产业的合作、科研跟教学的合作,都要加强起来。核心就是产学研中间有个三角区,就是产业和科研、教学的公共区域,我们需要增强,因为在这个区域里面才能对三个方面都是可以出得上力,可以对产业有所贡献。

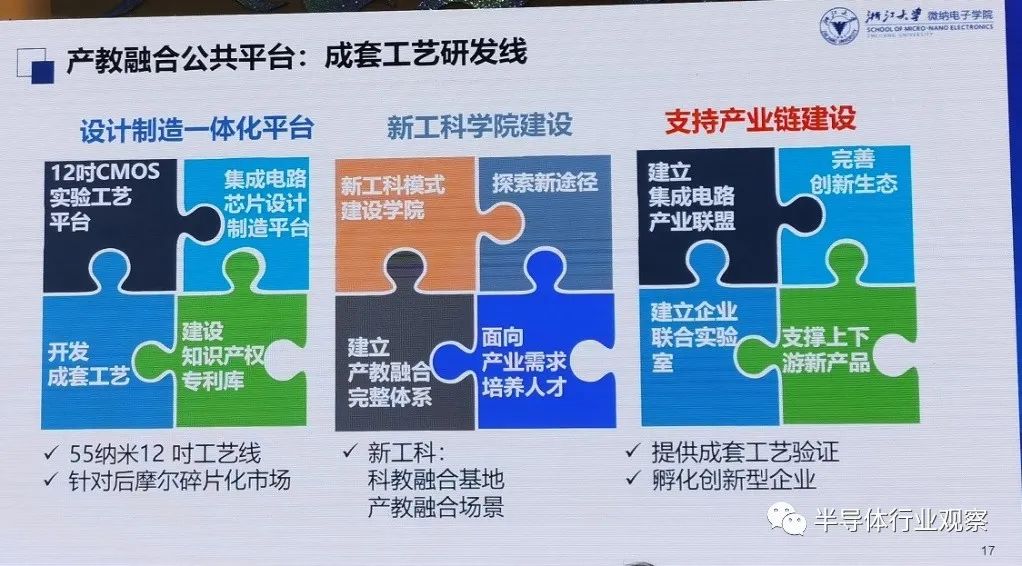

在这个思路下,我们在浙江大学做了一条生产线,一定要做成套工艺的公共平台,因为缺少了成套工艺,做产业的共性技术研发,我觉得是不可思议的,是很难的。在这个平台上,我们定位为一个12寸55纳米的试验线,这条线上最大的特点是设计制造一体化,因为原来浙江大学的设计能力还是比较强的,也对国家的产业做了很多贡献,我们把制造跟设计一体化,融为一体,对我们的产业可以做很多共性技术的研究。

另外,我们可以做个新工科学院的建设,让学生和老师有一个产教融合的平台,有个实习场景,我们可以想像,我在想,如果我们全国的集成电路专业学生、微电子的专业学生,大概现在是8、9千人,如果有机会把每个学生毕业之前能够到这个平台上,从设计制造走一下,我觉得对我们的学生培养一定是非常有好处的。所以我想这个新工科的建设,一定有它很好的前景。

另外,因为这是一条很小的线,它可以对我们的新产品、新材料、新装备提供一个试验的场所,因为你做一个新的材料、新的装备,脱离了成套工艺的支撑,你这个新的东西怎么才能用起来呢?所以这对国家产业链的发展一定有很大支撑作用的。

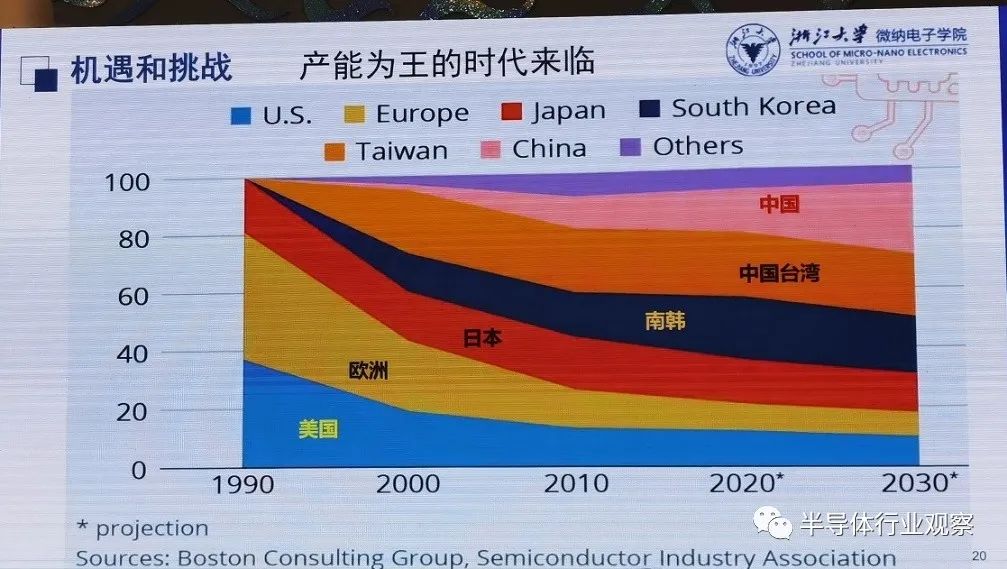

其实我今天讲的核心,我总觉得我们国家的集成电路对产业引领上还要大大加强,我们老是说我们的国家集成电路起点低,发展晚,其实不对,我们发展得很早,我们中国的第一块硅单晶1958就做出来了,第一块硅集成电路诞生是1965年,当时跟世界的差距也不大。但是随着产能到1000万块,1亿块,或者6亿块,到最后我们跟世界产业的先进技术水平差距就差了将近20年。所以就是产业引领,在我们整个集成电路领域里面,我觉得是不够。所以我始终认为,我们做研究只是手段,目的就是产业化,现在的王道就是产能,这其实是关联的。

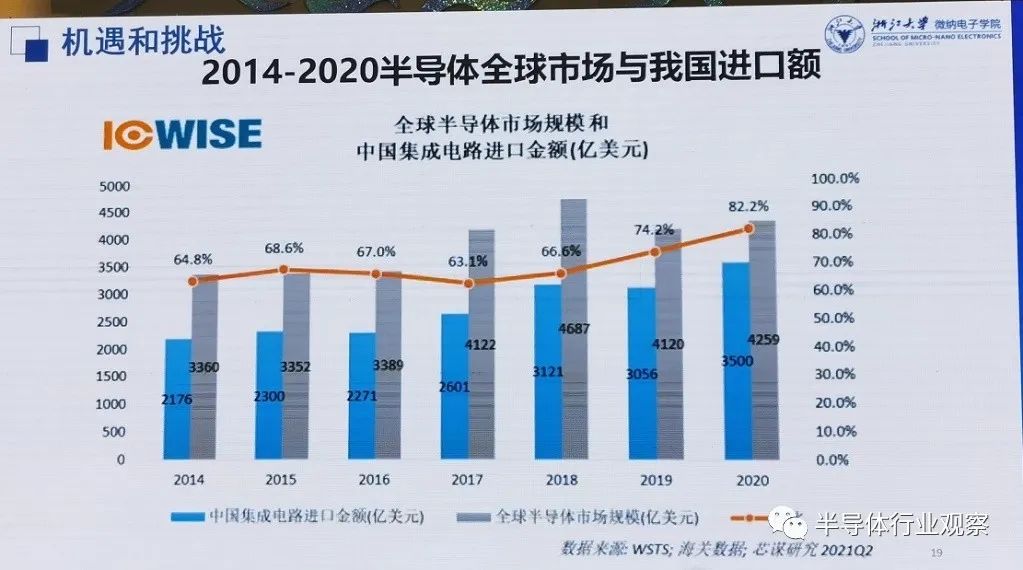

我刚才说,我们的产业引领做得不是很够,我们的产能提升这个王道没有抓住,导致的后果就是最近7年,《集成电路产业推进纲要》颁布有7年了,这7年以来,国内的芯片市场上的国产化率反而更小了,进口率反而变大了,这个数据我看到以后,心里就觉得很别扭,我们推进纲要出来7年了,但是芯片的国产化率没有上来,我总觉得是对“科研是手段,产业是目的,产能是王道”理解不够。

从产能来看,美国的产能近几年来一直在下降,欧洲也是在下降,日本基本上是维持,韩国和我们的台湾地区,产能在最近上升得很快,但是到2020年以后,预测产能提升不会那么快,就是我们中国的产能提升必须要加强。在我们先进技术还没有达到顶尖水平的时候,产能是不能放弃的。所以我觉得产能为王,大家现在已经看到这个结果了,对我们国家的影响真是非常大。所以现在说集成电路发展过热之类的,这个说法也未必正确,过热是因为烂尾楼的工程显得很过热,其实你要选到好的产品和方向,我们集成电路的需求是很大的,完全可以大大发展,核心就是说我们要寻找合适的方向,找到自己能做的事情嵌入进去。

总之,我国的集成电路芯片发展是非常艰辛的,后摩尔时代发展节奏下来了,给我们追赶者一个机会。我要强调的就是芯片的成套工艺是提供交叉学科发展的舞台,只有通过这个舞台,交叉学科才能体现它的价值。所以在产业引领方面,我觉得政府的各有关部门真的要重视,其实产业引领比科学引领更重要。回顾集成电路发展60年的历史,我们的科学技术在50年代也是蛮可以的,但是产业没有跟上去。

最后,再强调一下:科研是手段,产业是目的,产能是王道。