3月11日消息,晶圆代工领域走入先进制程技术,目前美国半导体巨头英特尔仍在为7nm制程研发伤透脑筋,全球晶圆代工龙头台积电与竞争对手、南韩科技大厂三星电子较劲,除了先进封装技术,制程采用技术更是市场焦点,三星声称将在3nm制程采用环绕闸极技术(Gate-All-Around,GAA),台积电则是考虑进入2nm制程才导入。外媒报导指出,台湾与日本半导体业界研发,将带来新一代晶体管,有望实现2nm制程。

据报道,日本产业技术综合研究所与台湾半导体研究中心(TSRI)合作,开发新一代晶体管结构。如果采用这项技术,这对于先进制程技术对于摩尔定律极限突破带来重大影响,这份多层键合与异质整合的研究有望带来可行性参考。

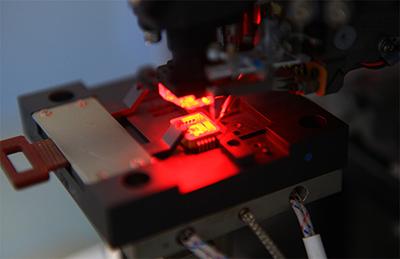

这项技术是将硅(Si)和锗(Ge)等不同材料从上下方堆栈,从「n型」和「p型」场效应晶体管(FET)靠近、名为「CFET」结构。日本产业技术综合研究所表示,这技术是全球创举。CFET结构晶体管效能更高、面积更小,有助于2nm以下制程的新一代半导体技术,预计在2024年以后运用,并在未来3年内提供民间企业技转。

台积电2月9日董事会决议,核准于日本投资设立一百分之百持股之子公司,实收资本额不超过日币186亿元(约美金1亿8,600万元),以扩展本公司之3DIC材料研究。台积电董事长刘德音提及,台积电在新材料技术创新,包括六方氮化硼(hBN)已接近实现量产,与台湾学界团队合作成功以大面积晶圆尺寸生长单晶氮化硼等。

刘德音先前接受2021年国际固态电路会议(ISSCC 2021)开场在线专题演说时指出,台积电3nm制程计划比预期早一些,未来主要制程节点将如期生产。台积电3nm制程预计今年下半年试产,明年下半年进入量产。

至于2nm制程,台积电将转向采用GAA的纳米片架构,提供比FinFET架构更多的静电控制,改善芯片整体功耗。

刘德音指出,系统整合是半导体未来发展方向,Chiplet是能让技术朝向正确方向发展的关键,而台积电SoIC先进封装技术可实现3D芯片堆栈。