作者:罗桂斌

一款好用的FPGA永远离不开强大的开发工具作为支持。对于设计FPGA的公司而言,设计出优秀的FPGA器件还不足以获得市场和FPGA开发人员的青睐。优秀的开发工具软件却能最快速度的讨好一线工程,培养他们的开发流程和使用习惯。一旦习惯了一款开发工具之后,再使用其他家的工具,只要不符合之前的经验就会觉得这个工具不好用、不人性。这种先入为主的情况,各大厂家也是心知肚明,所以才会积极的推进自家的器件在大学的推广。这些未来的FPGA工程师一旦适应了某一家的开发思想和流程,当他们走上工作岗位之后,也会毫不犹豫地选择自己熟悉的器件。培养自己的潜在客户,是面向未来的投资。

Quartus、Vivado和Diamond,相信前两个大家都比较熟悉,Diamond是Lattice的FPGA开发工具。Quartus和Vivado都是业界比较优秀的软件,可以完成FPGA从评估、设计、调试的各个环节。FPGA开发软件都是按照FPGA的开发流程来设计的,下面来简要回顾一下FPGA的开发流程:

- FPGA选型、资源和功耗评估;

- FPGA RTL代码、约束设计;

- RTL代码仿真和验证;

- FPGA版本集成和综合(Synthsis);

- 布局布线(Place and Route)和生成bitstream文件;

- 上板调试;

- 发布FPGA版本

以上各个环节其实都是可以在厂商提供的集成开发环境中完成的,Quartus和Vivado自然不用多说,相信大家再熟悉不过了。今天我们要看试用的主角-PDS是否能够完成以上各个环节的开发。

PDS的安装很容易,只要按照软件的安装教程操作即可。需要注意的是,PDS需要到紫光通创的官网(https://www.pangomicro.com/support/License-pds/index.html)申请PDS和Synplify的Node-lock Lisence,需要电脑网卡的MAC地址。官方审核通过之后,会以邮件附件的形式将Lisence发送给你。

PDS安装过程很顺利,然后打开一个demo工程led_test,功能是板上4个LED流水灯。重新综合和布局布线,然后下载,一切顺利,板上LED轮流点亮,试用结束!

如果就这样敷衍的试用一下肯定是不行的,作为一个专业的FPGA工程师,可是每天都要和开发工具斗争的,所以肯定要按照流程走一下,看看各个环节表现如何啊。

首先一般公司在开发一款产品的时候,FPGA设计可不是从零开始,大部分的代码都是复用和移植。所以在评估资源的时候都是先集成一个近似的版本出来,综合和布局布线,分析资源利用报告和功耗评估报告,初步评估资源的使用情况和功耗。在评估的基础上留出一定的裕量,比如30%;当然是按照资源占用率最多的一项资源,比如IO、BRAM或DSP等。

至于仿真验证就不用多说了,我从来没用过Quartus和Vivado里面的仿真器,因为都没有Modelsim/Questsim/VCS好用啊。实际上Quartus的仿真器关联的也是Modelsim。Vivado集成了自己的仿真器,但是我没用过(编译、仿真速度和可视化肯定不如Modelsim)。

那么我直接打开了一个ov5640_ddr_hdmi的demo工程,在这个基础上试试PDS。这里提示大家一下,打开help->HelpTopics,有关于PDS操作的说明文档。重点是中文!中文!中文!

RTL代码和约束开发

RTL代码开发没什么可说的,大家直接使用自己顺手的编辑器和插件就好了,FPGA开发工具里的文本编辑器没有一个是好用的。PDS的约束没有使用标准的sdc文件,而是一个fdc文件。但是语法都类似。如果不懂语法可以直接使用PDS的约束编辑器开发约束,常用的基本约束都有:时钟约束、输入输出延时和时序例外。引脚约束也可以在约束编辑器的Device->IO中设置,这一点跟Quartus一样,引脚比较多的时候可能工作量大一点,好在引脚约束只需要项目开始的时候编写一次就行了,之后创建新工程的时候直接把约束文件拷贝过来就行了。

综合(Synthsis)

综合器绝对是FPGA工具的核心组件,直接决定了综合出来的电路实现。即使是Intel和Xilinx这样的巨头在这方面做的也不是很好,综合速度和效率并不是最好的。Synopsys这家公司做ASIC设计的同行应该再熟悉不过了,Synopsys和Mentor是ASIC设计领域永远绕不过的两大家,其提供了ASIC全流程的开发工具。在FPGA/CPLD领域也一样,Synopsys的Synplify是各家开发工具都支持的第三方综合器。

PDS提供了两个综合器:ADS和Synplify,在Project Setting→Part中可以选择。ADS应该是PDS内置的综合器,Synplify是第三方综合器,需要在紫光同创官网申请OEM Lisence。那这两个综合器哪个更好一些呢?我很快得出了结论,下面来看两个综合器对同一个工程的综合结果。

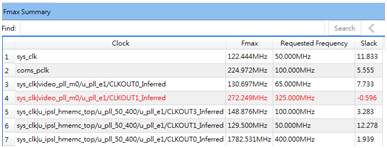

图1.ADS综合结果(上)Synplify综合结果(下)

这个工程的资源占用率并不是很高,但是ADS却有时序不过的情况,Synplify则没有出现时序问题。出于好奇,我还是打开了时序报告和Design Editor看看是哪里时序不过。又对比了一下Synplify同一个端口的路径有没有问题。

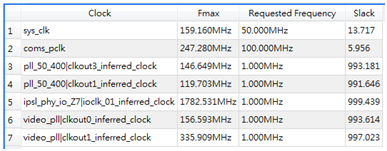

图2.资源利用率报告

图3.ADS最差路径(左)和Synplify最差路径(右)

虽然看起来差不多,但是结果还是说明Synplify会好一些,这也是官方为什么默认使用Synplify作为综合器的原因吧?

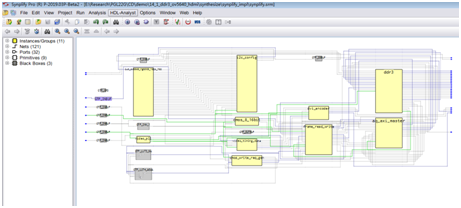

有时候在综合的时候不确定某些资源和信号是否被优化掉,偶尔会打开RTL视图(Schematic)看看连线和端口有没有别优化掉。使用不同的综合器,RTL 视图也是不一样的,Synplify会另外自动打开,ADS则还是在PDS里面。貌似还是Synplify好看一些呢。

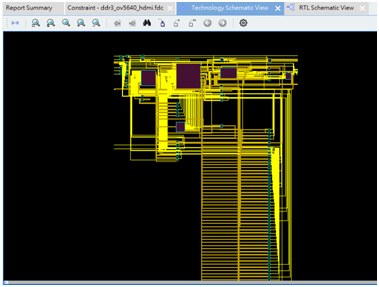

图4.ADS RTL视图

图5.Synplify RTL视图

布局布线(Place and Route)

其实在综合和布局布线中间应该还有一个步骤是-映射(Mapping),即把综合出来的电路映射成FPGA中的资源。但是在PDS中没有体现这一个步骤,咱也不知道,咱也不敢问。布局布线器也是FPGA开发工具中的核心技术,直接决定了能否布通和时序是否满足。布局布线的细节就不得而知了,但是可以对实际的布局布线结果进行一下分析。

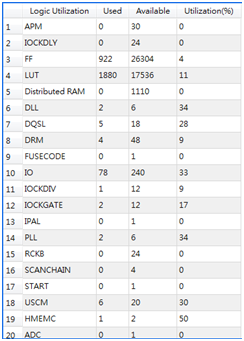

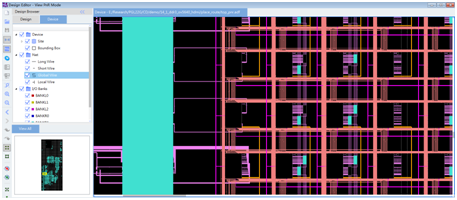

图6.工程布局布线结果

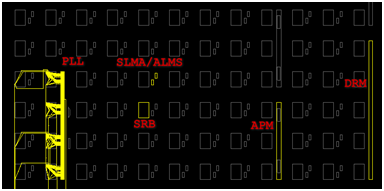

这里想要重点夸一波PDS的Design Editor功能,通过这个视图可以很清楚的看到FPGA内部资源的分布和架构。可以简单的看一下几个基本的资源排布。

图7.基本资源排布

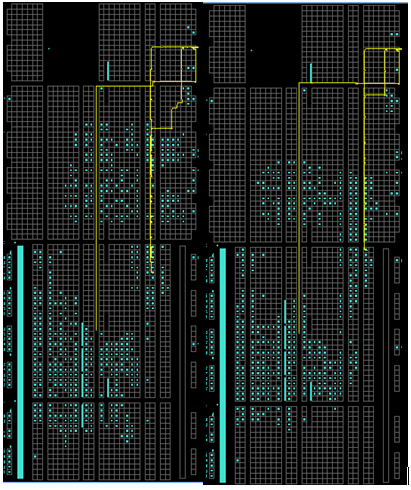

图8.布线资源

而且显示这么多的资源和布线,我这么差的机器一点也不卡,很流畅。想想Vivado打开Device View的时候,我要感动的哭了。

这里的FPGA基本资源中有一个很有趣的东西,叫做SRB(Signal Relax Block),我在官方手册里没有找到关于他的细节介绍,但是很明显他是负责完成FPGA内部走线互联的开关矩阵,相当于Xilinx FPGA的SwitchBox。每一个CLM旁边都有一个SRB,相信经过多少个SRB和每个SRB的内部走线延时会对时序有很大的影响。

在做时序优化的时候(一般由于时序裕量小或者时序不过),会看关键路径在哪里,然后通过在长路径中插入寄存器或者改变资源的位置来优化时序。在PDS中可以很容易的找到关键路径,只需要点击最差时序路径即可,这一点非常好用。

调试(Debugger)

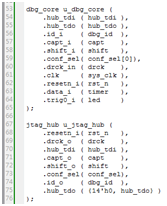

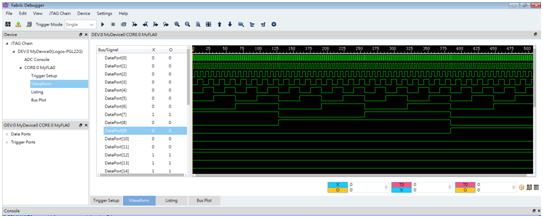

对于调试这一点,我可能要吐槽一下。在实际的项目调试的时候,很多条件和情况是没法通过仿真验证覆盖的,所以只能上板调试,然后抓FPGA内部的信号分析。PDS的调试功能对于有经验的工程师可能还好,但是对于初学者肯定是不友好的。要实现片上信号的触发捕获,首先要创建两个IP:debug_core和jtag_hub。debug_core需要设置触发信号和需要捕获的数据位宽等,然后将调试信号连接到debug_core;最后用jtag_hub连接到debug_core上。

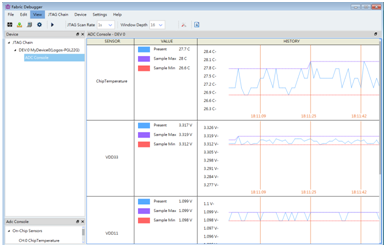

PDS需要打开Debugger,如果连接正确,在Scan JTAG的时候会识别到FPGA器件和内部的debug_core。点击触发就可以捕获到信号了。此外在debugger中也可以看到内部ADC监控的温度和核电压。这种用法和Vivado有点像,Vivado也提供可以直接在代码中例化的ILA IP。这要是没几年FPGA开发经验,这玩应真是不会玩。想想Vivado的Setup debug功能,综合后直接设置想要调试的信号即可,在Vivado中可以设置任意信号做为触发和触发条件,简直不要太好用。PDS这方面好好学学。

图9.ADC温度电压监控

图10.debug_core代码

图11.调试界面

写在最后

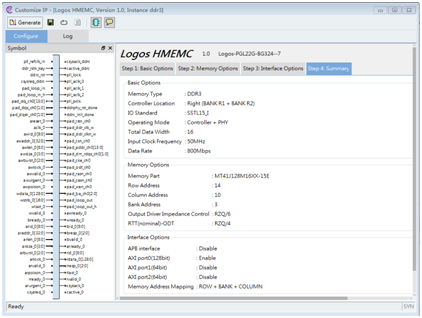

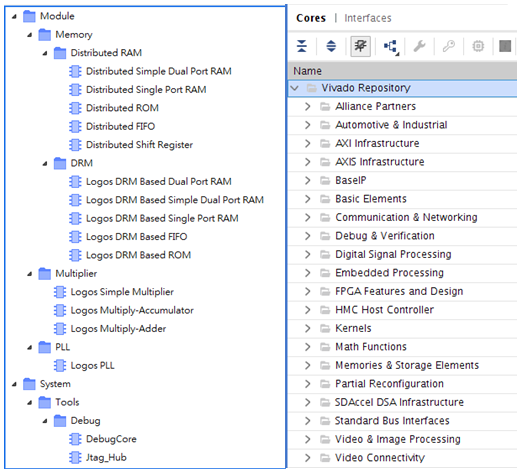

另外还有几个地方想要说一下,PDS提供的IP实在是太少,少到什么情况呢。只有基本的片上资源IP,PLL、RAM、FIFO、QUEUE、乘法器这些。连片上的DDR控制IP都没有集成在IP Compiler里面,需要另外导入。PGL22G内部集成了硬核的DDR控制器,这个是我比较感兴趣的,但是DDR的IP竟然没有集成在PDS里面,而且配置也略显麻烦,支持最多三组AXI,一组128bit位宽的,两组64bit位宽的。

图12.DDR控制器IP

跟Vivado对比一下,实在是差的比较多。

图13.PDS IP Compiler(左)Vivado IP Catalog(右)

这一点对于具有一定规模的公司来言还好,毕竟一些常用的模块都有内部开发的IP可以调用。但是对于白手起家的,可能初期的版本要花费较长的时间了。在IP配置界面可以点击datasheet,查看IP的使用方法,重点是中文!中文!中文!

写在最后,对于国产FPGA开发工具我的心里预期是比较低的。但是PDS绝对出乎我的意料,因为它不仅仅是能用,有些方面还是挺好用的。我第一次用PDS,大概用了三四个小时,已经可以熟练使用了,连debugger这么复杂的功能都玩起来了。要说紫光同创的FPGA是国货之光可能有点过,但是目前看来基本替代低端的国外FPGA应该问题不大。只要是紫光同创的FPGA在开发过程中没有潜在的坑,同时价格有优势,并且供货有保障的情况;说真心话,我非常愿意在下一个项目里使用Logos系列FPGA替换掉Lattice的XO2。

说的好像我说的算一样~