电子器件工程联合会(JEDEC)终于在今日正式发布了下一代主流存储器(DDR5 SDRAM)的最终规范。自 90 年代末以来,双倍数据速率(DDR)存储器技术已经历了多次迭代,并且推动了 PC、服务器等生态的快速发展。而最新的 DDR5 规范不仅再次扩展了 DDR 内存的功能,且速率也较上一代 DDR4 轻松翻倍。预计基于新标准的硬件,将于 2021 年陆续在服务器和 PC 客户端等设备上得到采用。

据悉,JEDEC 最初于 2018 年提出了 DDR5 的内存规范。虽然今日发布的正式版本来得有些晚,但并没有降低新一代存储器标准的重要性。

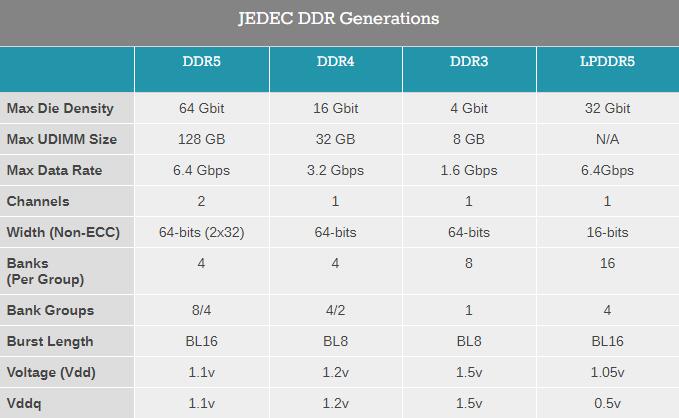

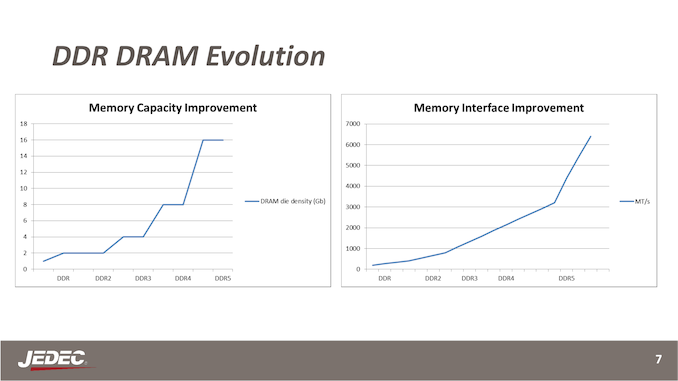

与往年的历次迭代一样,DDR5 再次将重点放在了 DRAM 存储的密度和速率上。JEDEC 将两者都提升了一倍,最大内存速率也设置到了 6.4Gbps 起步、单条 LRDIMM 容量有望达到 2TB 。

为了实现这一目标,业内一直在努力改进生态支持,比如让 DIMM 上的电压调节器和芯片级 ECC 校验做到更加精细。

与 DDR4 内存相比,DDR5 最直观的变化,依然体现在容量和密度上。经历了数年的设计研发,DDR5 标准已支持单颗 64Gbit 的 DRAM 存储芯片,是 DDR4 最大允许容量(16Gbit)的四倍。

结合管芯堆叠工艺,还可将多达 8 组管芯塞入单个芯片,那样 40 个单元的 LRDIMM 即可达成 2TB 的有效存储容量。至于不那么起眼的无缓冲 DIMM,典型双面配置亦可达成 128GB 的单条内存容量。

需要指出的是,相对于频率和带宽的提升,制造密度的提升要相对慢一些,但标准依然具有相当深远的前瞻性。对于内存制造商来说,今年已可使用 8Gbit 和 16Gbit 的芯片来制造 DDR5 内存。

从 DDR3 到 DDR4 的过渡,JEEDC 已让内存带宽从 1.6Gbps 提升到 3.2Gbps 。但是即将上市的 DDR5 产品,再次轻松地超越了 50%(至 4.8Gbps),未来更是有望达成 6.4Gbps 。

内存制造商之一的 SK 海力士预计,十年后可达成 DDR5-8400 。为实现这一目标,显然需要对 DIMM 的底层(比如内存总线)和配套的逻辑器件加以大量的改进。

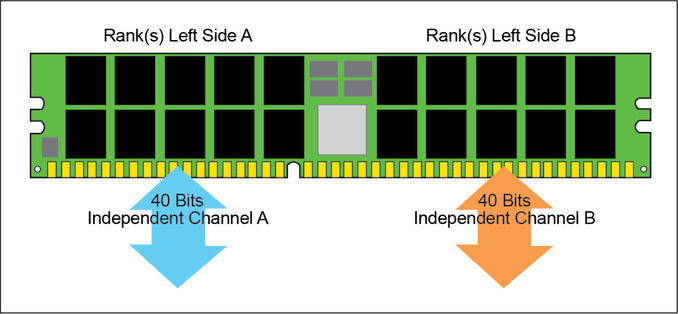

与我们在 LPDDR4 和 GDDR6 等标准中看到的情况类似,单个 DIMM 可被分解为两个通道。因为 DDR5 不会为每个 DIMM 提供一个 64-bit 数据通道,而是为两个独立的 32-bit 数据通道(ECC 则是 40-bit)。

与此同时,每个通道的突发长度从 8 字节(BL8)翻倍到了 16 字节(BL16),意味着每个通道可在每次操作时交付 64 字节,从而让有效带宽较 DDR4 时代增加了一倍。

对于标准的 PC 台式机平台而言,DDR5 系统可用 4 × 32-bit 的配置,来代替 DDR4 系统上的 2 × 64-bit 设置。内存条仍将成对安装,而不是回到 32-bit 的 SIMM 时代(但现在的最低配置是 DDR5 较小通道中的两个)。

这种结构上的变化,还在其它地方引发了一些连锁反应。比如 DDR5 引入了更高细粒度的存储器刷新功能,允许在使用某些存储器的同时刷新其它存储器,从而实现更快的刷新(给电容器充电)。

存储器的最大 Bank 数量也从 4 组翻倍到了 8 组,有助于减轻顺序内存访问带来的性能损失。

来源:cnBeta.COM