在集成电路领域,有一条被遵循了数十年的规律,那就摩尔定律,该定律表示,相同面积上集成的晶体管密度每两年翻一番,但保持产品售价不变。正式在这个定律的推动下,我们进入了当前这个高科技的现代社会。但进入近些年,因为硅材料因此,人们积极进行研究以研究新的有前途的半导体材料。用来替代硅。

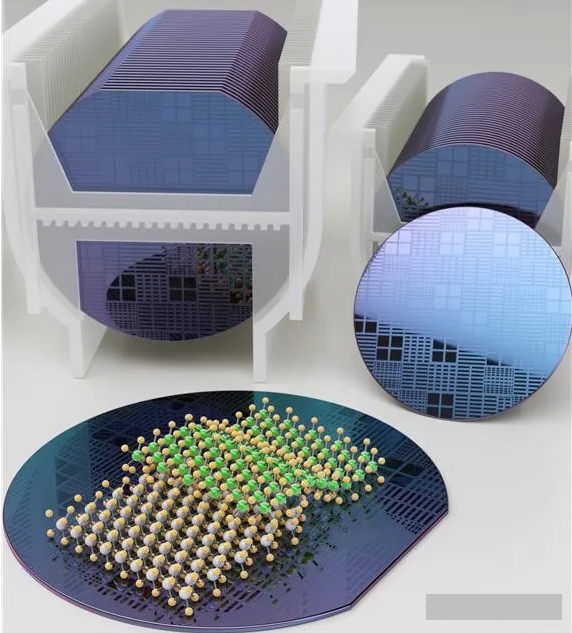

最近,由UNIST材料科学与工程学院的Soon-Yong Kwon教授领导的研究小组成功地对二维(2D)金属电极(metal electrode)进行了patterning,长期以来,二维电极一直被认为是实现高性能超细( ultra-fine )半导体的障碍。他们在直径为4英寸的硅基板上形成所需的形状。

为了改善半导体芯片的性能,我们必须使构成芯片的各个元件非常小。然而,在现有的基于硅的电子器件的小型化和集成化面临挑战。因此,使用诸如石墨烯这样的薄材料开发超越摩尔半导体至关重要。新的2D金属电极只有一个原子厚,因此可以应用于半导体器件的薄膜材料,例如石墨烯。据研究团队称,这有望加速半导体器件的小型化。

半导体器件只有在电子按其所需的特定位置和方向流动时才能正常工作。但因为你想把器件做得更小,在单位面积上集成更多的晶体管,所以你一直希望把晶体管变小,这时候电子将开始不按照我们的期望那样地流动,产生了所谓的隧道效应。为了应对这一挑战,近来对超薄2D半导体材料的使用进行了很多讨论,但尚未开发出适合于此的电极。

半导体的特性介于金属和绝缘体等普通导体之间。因此,如果仅改变半导体材料,则形成相对较高的势垒(即肖特基势垒),这使得电子传输变得困难。因此,为了实现高性能的超薄半导体器件,还必须新合成2D电极材料。

在这项研究中,研究小组报告了在不同基板上以晶圆级生产金属过渡金属二碲化物 (metallic transition metal ditellurides )patterned layers 的情况。根据研究小组的说法,“我们的二碲化钨(tungsten ditelluride)和二碲化钼层(molybdenum ditelluride layers)是通过对前体过渡金属层(precursor transition metal layer,)进行碲化(tellurization )处理而生长的,其电子性能可与机械剥离的薄片相媲美,并且可以与2D半导体二硫化物结合。”

“已经证实,向特定金属(如铜(Cu)或镍(Ni))中添加适量的碲(tellurium),即使在相对较低的温度下也会被液化,”该研究的第一作者,UNIST机械工程的Seunguk Song 说,他进一步指出,“我们的技术提供了一种简单有效的方法来生长高质量的过渡金属二碲化物,其电气性能可与机械剥落(mechanically exfoliated )的薄片媲美。”

根据研究小组的说法,所形成的金属-半导体结没有明显的无序效应(disorder effects )和FLP( Fermi-level pinning ),并且它们的SBH基本上遵循Schottky-Mott limit。新合成的2D电极材料在合成过程中几乎没有物理缺陷,因此表现出与机械分离的2D材料相当的优异物理和电性能。另外,整个过程中有几分钟是在低于500°C的温度下执行。由于可以在现有的半导体处理中实施,因此还降低了运营成本。

该研究小组还进行了将2D半导体二硫化钼(MoS 2)放置在新的2D电极上的实验。结果,金属与半导体之间的界面处的能垒(肖特基势垒)非常低,接近理论值,因此电子转移容易。在常规的半导体制造工艺中,注入离子以增加穿过能垒的电子的数量,并且该方法难以应用,因为器件变小并且电路线宽减小。然而,这次开发的电极材料可以在没有这种工艺的情况下提高半导体结中电子转移的效率。

Professor Kwon说:“由于新合成的金属电极和半导体结的缺陷很少,因此遵循了理想的Schottky-Mott条件。” “特别是,有可能控制能垒(Schottky Barrier),这比通过商业金属布线技术实现更难,但这将有助于通过以下方式实现具有N型和P型两性的下一代半导体进一步的研究。”

这项研究得到了韩国科学技术部(MSIT)资助的韩国国家研究基金会(NRF)的纳米材料技术开发计划的支持。