该款新产品是佳能半导体光刻机产品线中,首个可对应大型方形基板的面向后道工序的光刻机。该产品配备佳能自主研发的投影光学系统,在实现大视场曝光的同时,还能达到1.0微米的高解像力。因此,在使用可降低数据中心CPU或GPU等能耗的有机基板的PLP4封装工艺中,新产品将可以实现使用515×510mm大型方形基板进行高效生产的用户需求。由于该产品具有高解像力、大视场曝光性能以及高产能,因此在实现半导体封装5的进一步细微化和大型化的同时,还可以降低成本。

■ 可满足高产能大型基板的封装需求

为了满足使用方形基板进行封装工艺的需求,佳能开发了可以搬送515×510mm大型方形基板的新平台。另外,针对在大型方形基板上容易发生的基板翘曲的问题,通过搭载新的搬送系统,可在矫正10mm大翘曲的状态下进行曝光。因此,新产品实现了高效生产大型半导体芯片的PLP工艺,可应对要求高产能的用户需求。

■ 实现1.0微米的解像力,对应高端封装

佳能自主研发的投影光学系统可实现52×68mm的大视场曝光,达到了方形基板封装光刻机中高标准的1.0微米解像力。因此,实现了应对半导体芯片的高集成化、薄型化需求的PLP等高端封装工艺,且可满足各种用户需求。

<参考>

■ 什么是半导体光刻机的后道工序

在半导体器件的制造过程中,半导体光刻机起到“曝光”电路图案的作用。通过一系列的曝光,在硅片上制造半导体芯片的过程称为前道工序;保护精密的半导体芯片不受外部环境的影响,并在安装时实现与外部电气连接的封装过程称为后道工序。

■ 什么是PLP

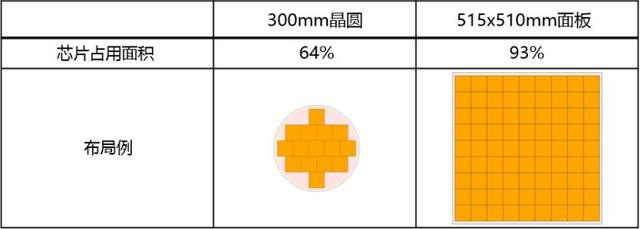

PLP是Panel Level Packaging的缩写,是指将多个半导体芯片排列在一个薄型方形大尺寸面板上并一次成型模制的封装制造方法。与普通的300mm晶圆相比,可以一次性高效地将许多半导体芯片放置在晶圆上,从而实现高产能。

<半导体光刻机的市场动向>

随着近几年物联网的发展,在半导体器件制造中,封装基板变得越来越集成化,也越来越薄。例如,由于高性能CPU或FPGA连接到多个高速大容量存储器,因此用于数据中心的高性能AI芯片的封装,有集成化和大型化的发展趋势。作为先进的封装技术之一,PLP不仅支持半导体器件的高度集成和薄型化,而且还通过大型基板的应用实现了高产能,作为一种前景明朗的技术而备受关注。PLP通常用于制造追求高速处理的尖端半导体器件,例如AI芯片、HPC6等。(佳能调研)

1 为方便读者理解,本文中佳能可指代:佳能(中国)有限公司,佳能股份有限公司,佳能品牌等

2 使用了i线(水银灯波长 365nm)光源的半导体曝光装置。1nm(纳米)是10亿分之1米。

3 1微米是100 万分之 1米。(=1000 分之1mm)

4 Panel Level Packaging的缩写。将多个半导体芯片排列在一个薄型方形大尺寸面板上并一次成型模制的封装制造方法。

5 保护精密的半导体芯片不受外部环境的影响,并在安装时实现与外部的电气连接。

6 High-Performance Computing的缩写。指使用计算机执行计算量极大的处理。