作者简介

汪炼成,物理电子学博士,中南大学特聘教授,博士生导师,微电子科学与工程系副主任,高性能复杂制造国家重点实验室研究员。博士毕业于中科院半导体研究所, 先后在新加坡南洋理工大学,新加坡科技大学和英国谢菲尔德大学从事博士后研究工作,科研方向为第三代半导体电子/光电子器件和系统集成。

一、一起来学习下异质集成1.异质集成的定义

什麽是异质集成呢?顾名思义,就是把不同的物质集成到一起的技术。比较权威的官方解读,可以参考IEEE Electronic Package Society公布的Heterogeneous Integration Roadmap对异质集成的定义:“Heterogeneous Integration refers to the integration of separately manufactured components into a higher-level assembly (System in Package–SiP) that, in the aggregate, provides enhanced functionality and improved operating characteristics.”但因为是出自IEEE Electronic Package Society,所以上述异质集成更多从封装集成的角度来定义,即将单独制造组件集成为更高级别的组装体(SiP)。

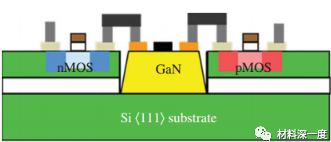

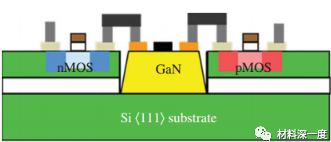

而在诸多文献报道中,异质集成并不限于封装领域,延伸到了器件甚至材料生长的范畴。如Jose Millan通过制作p型SiC层和SiC MOSFET,实现温度传感器和功率半导体在器件层面的异质集成(IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 9, SEPTEMBER 2014)。而雷声公司等报道先由嵌入III-V族化合物组成模板层,而后在模版上分区外延生长高质量的III-V族器件和标准硅基互补金属氧化物半导体(CMOS),从而实现在材料层面的III-V族器件和硅基CMOS的异质集成。以上两者一般都称为单芯片异质集成,类似于片上系统(SoC)的概念。

晶圆级外延层转移则介于上述SiP和SoC之间:如IHRL公司在InP衬底晶圆上先外延生长InP基双异质结晶体管(DHBT)外延层,随后通过载片将刻蚀去掉衬底后的DHBT外延层转移键合到已制作好的Si CMOS衬底上。

此外,狭义的异质集成,是将不同功能的芯片通过封装和半导体制造工艺限制集成在硅晶圆上,目的是将成熟硅技术应用到集成光子、集成功率器件、集成MEMS和传感器等各种不同领域。而广义的异质集成则是将任何不同功能的组件集成,实现性能的提升和功能的扩展。

图1 芯片和晶圆级异质集成

2.异质集成的定义注意要点

综上来看,异质集成的定义我觉得需要注意三点:

首先,异质集成是指两个或多个具有独立功能组件的集成。比如异质集成系统的p型SiC层和SiC MOSFET,GaN基HEMT和Micro-LEDs都具有独立的功能。但如果其中一部分不具有独立功能,则不能说是异质集成。比如,Ga2O3导热系数极低(0.11 W/(m*K),作为对比,金刚石为1300-2400,SiC为 490, GaN 为3.3, Si为150),散热能力成为氧化镓功率器件应用的最大瓶颈。西安电子科大的郝跃院士首次将晶圆级β-Ga2O3单晶薄膜(< 400 nm)与高导热的Si和4H-SiC晶圆级集成,并制备出高性能器件(International Electron Devices Meeting, IEDM,First Demonstration of Waferscale Heterogeneous Integration of β-Ga2O3 MOSFETs on SiC and Si Substrates by Ion-Cutting Process)。这是典型异质集成,β-Ga2O3晶体管和Si和4H-SiC衬底分别具有独立功能,异质集成实现β-Ga2O3晶体管散热性能,从而器件性能的提升。但是如果是在Si和4H-SiC衬底上生长β-Ga2O3薄膜,我觉得不能称之为异质集成,因为此时Si和4H-SiC只是作为β-Ga2O3生长的衬底,不具有独立功能,它们是β-Ga2O3晶体管器件的一部分。

其次,异质集成有层界限定。因为如果钻牛角尖的话,几乎任何产品都是异质集成的产物,比如电脑就是由CPU、内存、主板和硬盘等“异质”集成。所以需要异质集成进行层界限定。默认异质集成的最高层界限定就是封装体,即SiP级封装,如小芯片微米级组装等。往下包括晶圆级外延层转移的混合异质集成和单片异质外延生长的芯片级异质集成。

图2 SiP异质集成

图3 Raytheon公司GaN HEMT–Si CMOS异质集成

异质集成中“异质”同半导体物理和器件中异质结中的“异质”还是有所区别:异质结是针对不同半导体材料,而异质集成是针对不同功能组件。异质集成可以是同一种材料的不同功能器件的集成。

第三,异质集成和功能复用有区别。功能复用指的是兼容设计同一个器件或组件,使其具有不同的功能。功能复用为“一材多用”,而异质集成更多为“多材一用”。功能复用并不是异质集成。如GaN基LED作为光源器件,可以用于照明、显示和可见光通信功能。设计GaN基LED器件系统可实现多功能复用,如显示通信、照明通信、显示照明甚至显示照明通信,代表课题组有英国University of Strathclyde的Prof Martin Dawson课题组等。

3.异质集成的目的

从定义看,异质集成的目的主要是实现性能提升和功能集成拓展。

异质集成发展的一个最主要驱动力就是Moore’s Law下Si CMOS晶体管不断缩小至近极限值造成集成电路的互连延迟效应及能耗问题,和对More than Moore超越摩尔的强烈需求。其中最主要的便是硅基光子学。光子信息技术理论上具有更大的带宽、更高的速率和更小的功耗。但硅半导体材料为间接带隙,不能制作光源器件,这是其显著缺点。硅光能结合成熟Si基CMOS集成电路的强大基础和光子信息的优点,把光和电异质集成在一个芯片上,用来实现对光的驱动和探测,受到学术界和产业界的广泛看好。硅基光子学系统,包括光源、光调制器、光波导、波分复用器(WDM)、光电探测器等分立有源或无源器件。信息的快速准确处理需求对以上各个分立器件都提出了很高的要求,如在高频调制下仍然可以单模工作的动态单模(DSM)激光器光源等。

二、国内外主要进展

国内的中国科学院半导体所王启明院士、王圩院士、余金中研究员、黄永箴研究员、祝宁华研究员等研究组在InP基、硅基衬底上光子集成和封装技术上有长期的积累和较多成果。美国雷声公司、惠普公司及比利时的IMEC微电子研究中心在这方面研究世界领先。IMEC也是全球微电子集成技术方面高校科研和产业承转的典范机构。华为是光电集成通信芯片的全球领先企业,在前段发布了推出业界首款800G可调超高速光模块,单纤容量达到48T,这个传输容量意味着完成100部全4K版本电影的下载,仅需要1秒钟。

DARPA 对DAHI(Diverse Accessible Heterogeneous Integration)制造项目进行立项支持,每个公司提供自己最熟悉的产品和技术,汇集到其中某个芯片制造厂,实现异质集成。比如硅基化合物半导体材料(COSMOS)项目通过将InP异质结双极晶体管(HBT)与亚微米硅基CMOS实现异质集成,诺格公司提供InP技术、格罗方德半导体公司提供硅基CMOS原料、HRL实验室提供GaN、Nuvotronics公司提供3D波导架构的高Q值无源滤波器,诺格公司提供集成制造设计包,将这些材料和器件汇集到诺格的芯片制造厂进行制造。这样异质集成的优点时可以分别对各器件进行优化,提高设计开发的效率。

在“8K显示+5G通信”的应用前景推动下,基于第三代半导体GaN基 Micro-LED(光)和GaN基HEMT(电)原位单芯片光电异质集成在近年得到学术和产业界的关注。英国谢菲尔德大学Tao Wang教授,香港科技大学Kei May Lau教授,国内中科院半导体所和南方科技大学等课题组在这方面进行了深入探索。GaN LED当然也可和Si CMOS等功能单芯片集成。南京邮电大学和中科院苏州纳米所课题组在GaN基光源、波导和探测器片上光通信集成做出很多工作。

受物联网、智慧城市和医疗健康等产业的需求,基于MEMS和传感器的异质集成系统近年在科研和产业上都备受青睐,实现对振动、温湿度等各种环境因素和血糖、心率等各项人体健康指标的传感监测。环境和人体的多参数复杂特性需要集成不同类型的传感器和数据处理器。斯坦福大学鲍哲南教授团队研发的电子皮肤就是一个复杂的异质集成系统,包括疼痛感受器,冷热感受器和机械刺激感受器等传感器以及读出矩阵等数据的高效采集和传输系统等。

实现高效散热,提高器件性能是异质集成的另外一个主要目的。单独一种材料或器件不一定同时兼具高功能性能、高散热性能。特别高功率、高温第三代半导体器件尤其需要高效散热。如前述西安电子科大的郝跃院士将β-Ga2O3器件与Si和4H-SiC集成,实现高效散热,提高器件性能。2017年英国金刚石和碳化硅材料计划,支持富士通公司在金刚石和碳化硅衬底散热技术方面取得进展,同时支持布里斯托尔大学研发能满足未来高功率射频和微波通信的下一代GaN技术,金刚石基氮化镓(GaN)微波器件,金刚石的主要功就是散热。在“新基建”5G通信中扮演重要角色的GaN射频器件,特别是用于宏基站的100W-300W级的极大功率GaN射频器件对散热要求很高,也需要集成到更高导热性能的散热基板上。

三、异质集成的挑战

异质集成存在协同设计、关键制造工艺、热应力管理、散热和可靠性、测试等方面挑战。异质集成设计包括前向设计,针对不同尺度(系统级、芯片级、材料级),不同物理机理(热、电、光、力学),和不同材料体系(金属、绝缘体、半导体、有机物)等进行协同设计,建立各个层级,不同结构材料部分的传递影响关系,对集成系统的服役性能进行全局优化。如GaN基LED照明、显示和通信多功能系统就面临高效高显色性、高分辨率高对比度和高速宽带宽的性能集成,大功率、高密度和高频驱动的结构集成等设计挑战。异质集成设计也可以逆向设计,考虑到系统的最低性能需求和理论上最大短板,有的放矢设计。前向设计,有点像婚恋中男女双方先看双方优点,而逆向设计则是各自亮出可接纳底线。

异质集成系统制造面临三维/曲面/柔性复杂结构形态集成,以及更小尺寸更高集成度(比如传感MEMS系统)的制造方面挑战。不同材料由于具有不同的热膨胀系数等(Thermal expansion coefficient, TEC),异质集成系统面临热应力循环加载带来的失效风险。一些先进散热技术,如芯片内微流道、芯片间微流道散热技术、相变散热技术,以及更高热性能的热界面材料和散热材料在广泛研究,以提高系统的热可靠性。

四、总结

第三代半导体器件的异质集成研究主要有:GaN基LED/LD等同Si基CMOS/GaN HEMT集成;GaN 基光源光波导探测器片上光通信集成和柔性集成;GaN MEMS和传感器集成;SiC MOSFET和传感器集成;极大功率GaN射频器件和β-Ga2O3电子器件同散热衬底集成等。

异质集成是指在一定层界(单芯片级、多芯片级或封装体级)上,具有独立功能的两个或多个组件的集成,目的为实现功能集成扩展或性能提升。异质集成和功能复用有区别。异质集成存在协同设计、关键制造工艺、热应力管理、散热和可靠性、测试等挑战。有效异质集成可实现“1个苹果+1个苹果≥2个苹果”的效果。

更多关于异质集成可参考IEEE Electronic Package Society公布的Heterogeneous Integration Roadmap,以及相关文献资料(Kazior, T. Philosophical Transactions of the Royal Society A, 372(2012), 20130105-20130105. (2014)等)。